Visible to Intel only — GUID: ykz1637227302928

Ixiasoft

2.4.2. Test Description

The simulation only checks for the assertion of trs_locked signal and the number of transceiver reconfiguration triggered after every video standard switching.

The following figure shows the sequence of the video standard for triple-rate design:

The following figure shows the sequence of the video standard for multi-rate design:

For single-rate design, there is one video standard being tested:

- HD single-rate – HD

- 3G single-rate – 3G Level A 10-bit Multiplex

If you turn on the Dynamic TX Clock Switching option, only one video standard is being tested with two different TX PHY reference clocks to demonstrate the switching.

- HD single-rate – HD

- 3G single-rate / triple-rate – 3G Level A 10-bit Multiplex

- Multi-rate – 12G 10-bit Multiplex Type 1

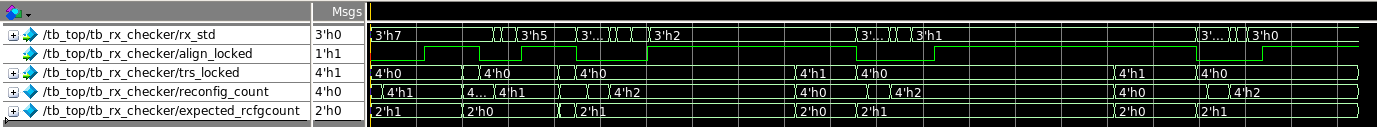

Figure 28. Simulation Waveform

| Testbench signal | Description |

|---|---|

| /tb_top/tb_rx_checker/rx_std | Video standard keep switching after obtaining lock signal |

| /tb_top/tb_rx_checker/align_locked | Lock signals from IP core |

| /tb_top/tb_rx_checker/trs_locked | |

| /tb_top/tb_rx_checker/reconfig_count | Actual number of transceiver reconfiguration triggered after every video standard switching versus the expected number of configurations. |

| /tb_top/tb_rx_checker/expected_rcfgcount |

A successful simulation ends with the following message: