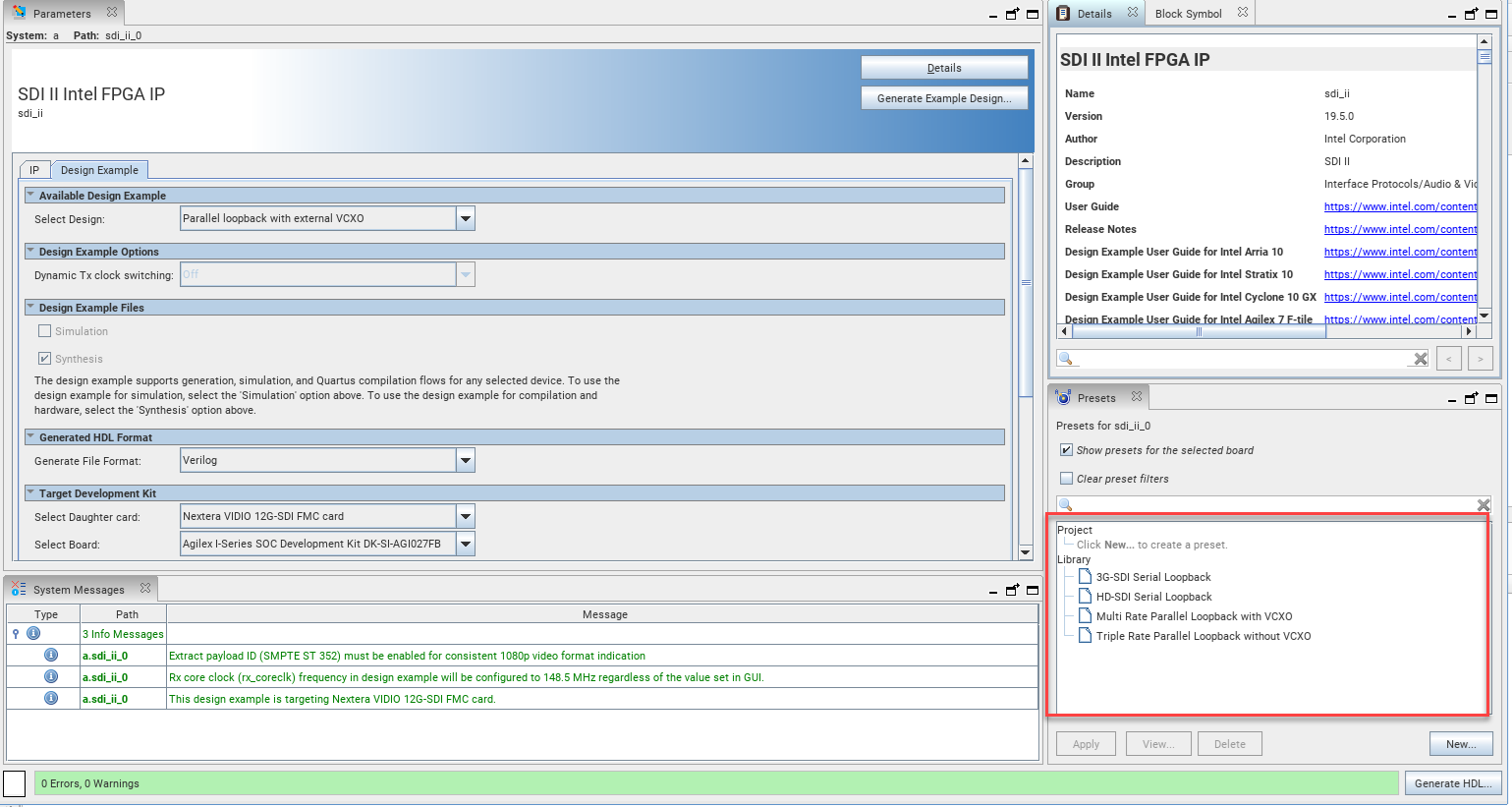

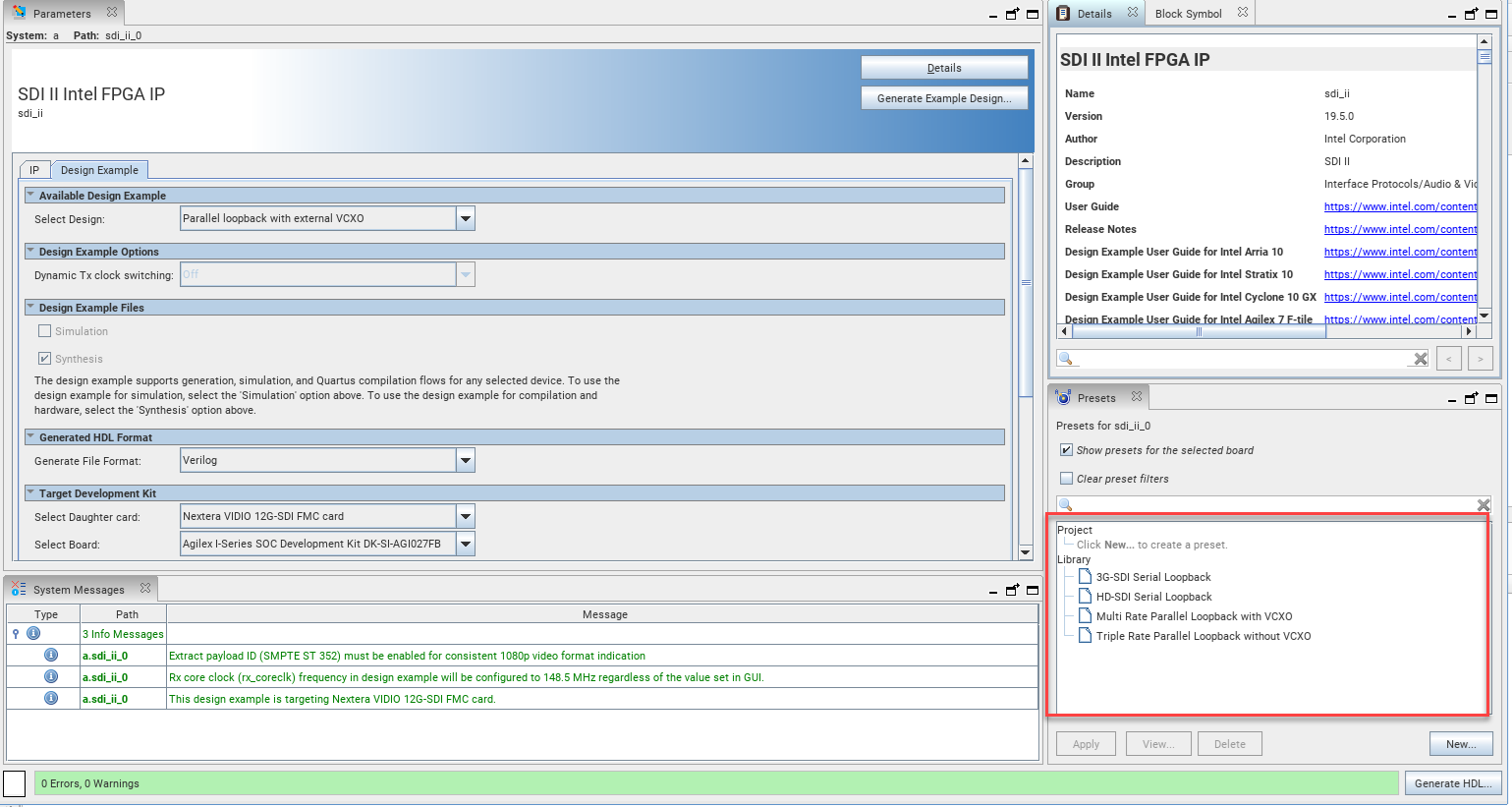

1.5.1. Design Example Presets

The Parameter Editor includes four design example presets using different video standards that you can use to pre-configure the IP and target your device development kit and Nextera daughter card directly. Hover over a preset for its description.

| Preset | Parameter Settings |

|---|---|

| 3G-SDI Serial Loopback |

|

| HD-SDI Serial Loopback |

|

| Multi Rate Parallel Loopback with VCXO |

|

| Triple Rate Parallel Loopback without VCXO |

|

Figure 12. Location of the Design Example Presets in the Parameter Editor