1.4. Compiling and Testing the Design in Hardware

Figure 8. Compiling and Testing the Design Flow

To compile and run a demonstration test on the hardware design example, follow these steps:

- Open the Quartus® Prime project (sdi_ii_agi_demo.qpf) located in Quartus directory.

- To perform Quartus® Prime compilation, click .

- Connect the Nextera SDI daughter card to FMC port A on the development kit.

- For parallel loopback designs, connect the BNC RX connector (J1/12G In) to an external video source and connect the TX connector (J2/12G Out) to a video analyzer. For serial loopback designs, connect the BNC TX connector (J2/12G Out) to RX connector (J1/12G In) or a video analyzer.

- Ensure all the switches on the development kit are in their default position. Refer to the Agilex™ 7 I-Series Transceiver-SoC Development Kit User Guide for more information.

If you are generating a parallel loopback with external VCXO design example, toggle DIPSW S10.2 onboard to OFF position.

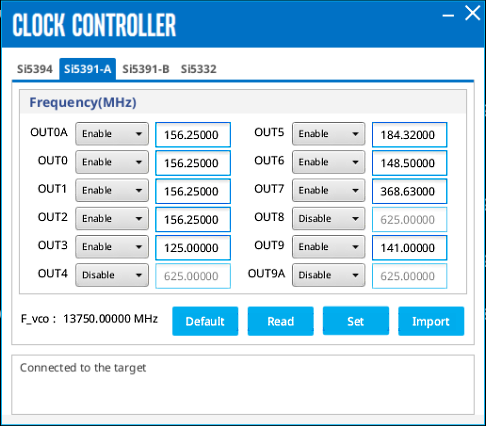

- Open Clock Controller and navigate to the Si5391-A tab. Set Out9 frequency to:

- Parallel loopback without external VCXO – 141.00000 MHz

- Dynamic Tx clock switching is enabled – 148.35160 MHz

Figure 9. Setting Out9 frequency in Clock Controller

- After the compilation completes, open Programmer and program the generated .sof file to the development kit.

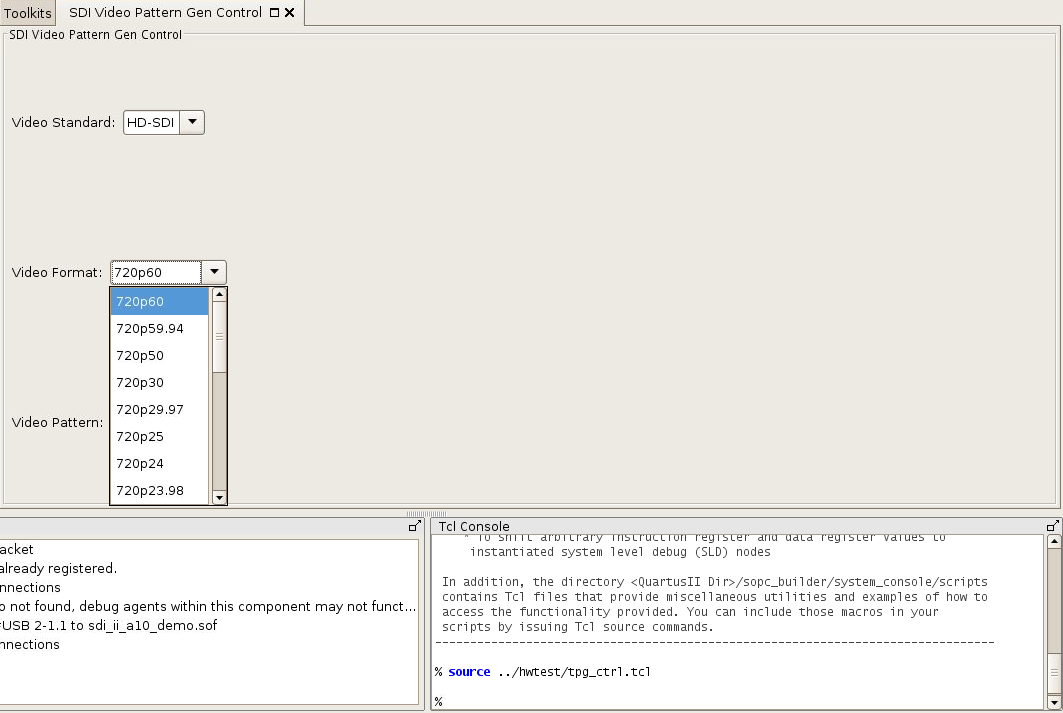

- For serial loopback designs, open System Console to control the internal video pattern generator.

- Go to and click System Console.

- After the initialization, type source ../hwtest/tpg_ctrl.tcl to open the pattern generator control UI.

- Select your desired video format through the UI.

Note: To allow segmented frame video formats (1080sF30, 1080sF25) and interlaced video formats (1080i60, 1080i50) to be correctly differentiated in an external analyzer, insert Payload ID in the serial loopback design.Figure 10. Selecting Video Format Through System Console

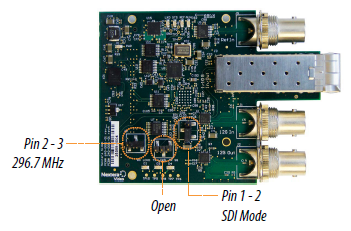

- The analyzer should be able to display the video generated from the source. Refer to jumper settings in the Jumper Settings and Descriptions table to change the jumper (J8) position before switching between fractional frame rate and integer frame rate video format. Press the push button (PB0) to trigger a device (LMK03328) power cycling through the PDN pin every time you change the jumper (J8) position.

Figure 11. Jumper Settings on Nextera 12G-SDI FMC Daughtercard

| Jumper Block | Description | Setting |

|---|---|---|

| J7 | Programming Header | - |

| J8 | To switch the generated clock frequency to TX channel:

|

1-2: 297 MHz 2-3: 297/1.001 MHz |

| J9 | To select SDI or IP mode:

|

1-2 |