Visible to Intel only — GUID: itm1475676657491

Ixiasoft

Visible to Intel only — GUID: itm1475676657491

Ixiasoft

1.2. Features of the Intel Arria 10 SoC Development Kit Reference Platform

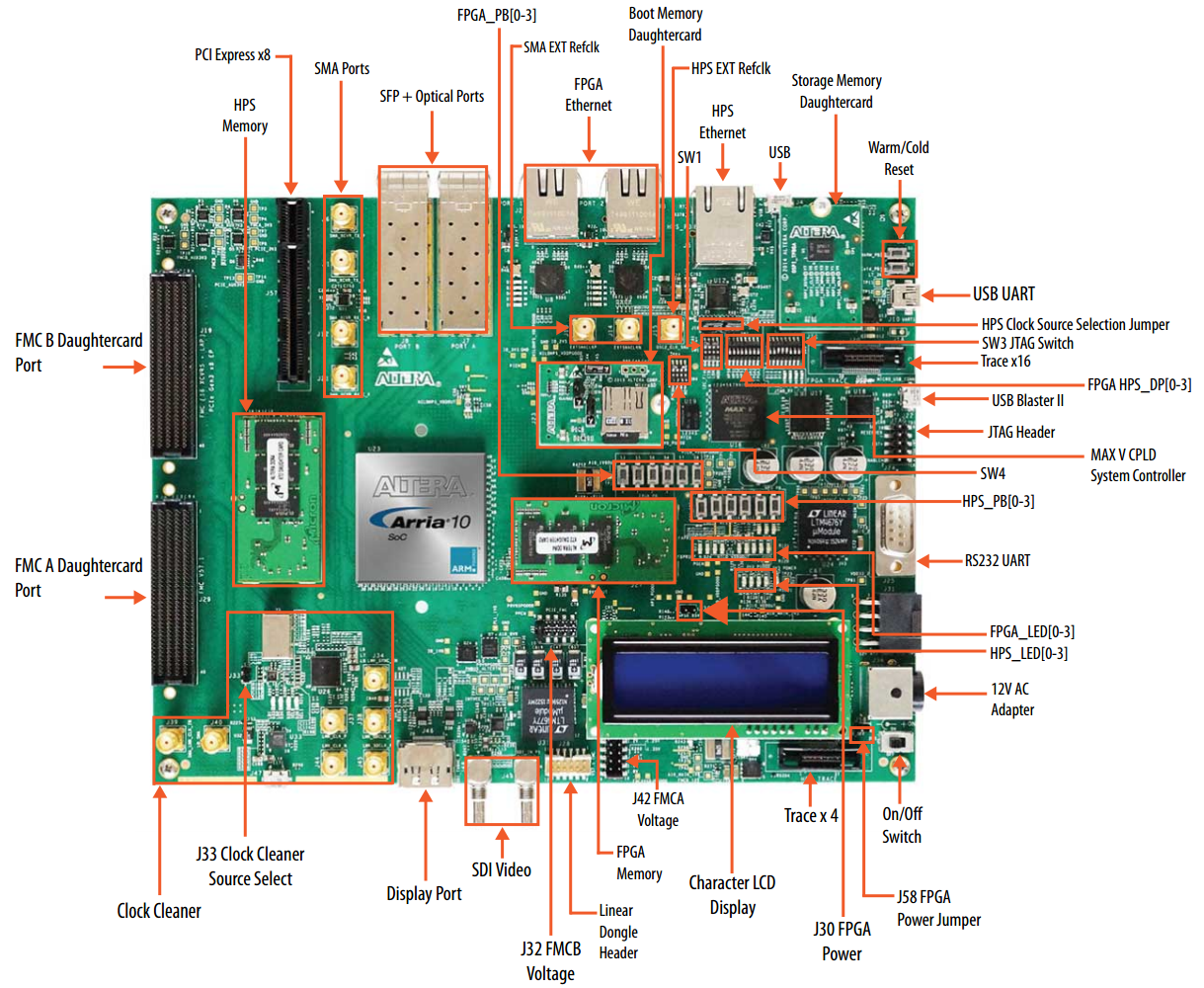

The Intel® Arria® 10 SoC Development Kit Reference Platform targets a subset of the hardware features available in the Intel® Arria® 10 SoC Development Kit.

Features of the a10soc Reference Platform:

- OpenCL Host

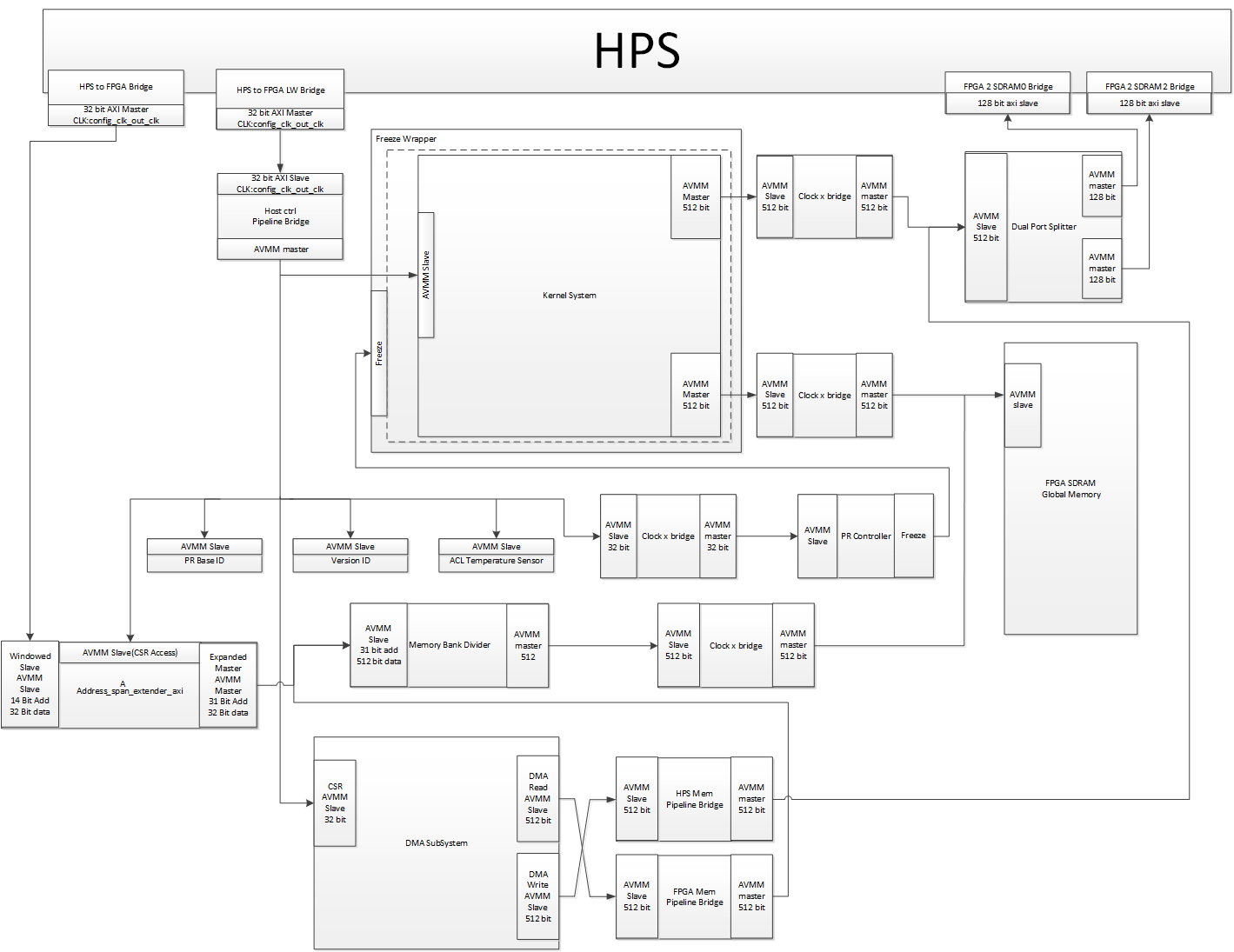

The a10soc Reference Platform uses the Intel® SoC HPS as the host that connects to the FPGA fabric via HPS-to-FPGA (H2F) and FPGA-to-HPS (F2H) bridges.

- OpenCL Global Memory

The hardware provides two 1-gigabyte (GB) DDR4 SDRAM daughtercards that are mounted on the HiLo connectors (HPS Memory and FPGA Memory in Figure 1).

- FPGA Programming via Partial Reconfiguration (PR) over HPS lightweight bridge (Lw-bridge)

- Guaranteed Timing

The a10soc Reference Platform relies on the Intel® Quartus® Prime Pro Edition compiler to provide guaranteed timing closure. The timing-clean a10soc Reference Platform is preserved in the form of a precompiled post-fit netlist (that is, the base.qdb Intel® Quartus® Prime Partition Database File that is part of the base.qar Intel® Quartus® Prime Archive File). The Intel® FPGA SDK for OpenCL™ Offline Compiler imports this preserved post-fit netlist into each OpenCL kernel compilation.