Visible to Intel only — GUID: sss1466499088458

Ixiasoft

1. Intel® Stratix® 10 Configuration User Guide

2. Intel® Stratix® 10 Configuration Details

3. Intel® Stratix® 10 Configuration Schemes

4. Including the Reset Release Intel® FPGA IP in Your Design

5. Remote System Update (RSU)

6. Intel® Stratix® 10 Configuration Features

7. Intel® Stratix® 10 Debugging Guide

8. Intel® Stratix® 10 Configuration User Guide Archives

9. Document Revision History for the Intel® Stratix® 10 Configuration User Guide

2.1. Intel® Stratix® 10 Configuration Timing Diagram

2.2. Configuration Flow Diagram

2.3. Device Response to Configuration and Reset Events

2.4. Additional Clock Requirements for HPS, PCIe* , eSRAM, and HBM2

2.5. Intel® Stratix® 10 Configuration Pins

2.6. Configuration Clocks

2.7. Maximum Configuration Time Estimation

2.8. Generating Compressed .sof File

3.1.1. Avalon® -ST Configuration Scheme Hardware Components and File Types

3.1.2. Enabling Avalon-ST Device Configuration

3.1.3. The AVST_READY Signal

3.1.4. RBF Configuration File Format

3.1.5. Avalon-ST Single-Device Configuration

3.1.6. Debugging Guidelines for the Avalon® -ST Configuration Scheme

3.1.7. IP for Use with the Avalon® -ST Configuration Scheme: Intel FPGA Parallel Flash Loader II IP Core

3.1.7.4.1. PFL II IP Recommended Design Constraints to FPGA Avalon-ST Pins

3.1.7.4.2. PFL II IP Recommended Design Constraints for Using QSPI Flash

3.1.7.4.3. PFL II IP Recommended Design Constraints for using CFI Flash

3.1.7.4.4. PFL II IP Recommended Constraints for Other Input Pins

3.1.7.4.5. PFL II IP Recommended Constraints for Other Output Pins

3.2.1. AS Configuration Scheme Hardware Components and File Types

3.2.2. AS Single-Device Configuration

3.2.3. AS Using Multiple Serial Flash Devices

3.2.4. AS Configuration Timing Parameters

3.2.5. Maximum Allowable External AS_DATA Pin Skew Delay Guidelines

3.2.6. Programming Serial Flash Devices

3.2.7. Serial Flash Memory Layout

3.2.8. AS_CLK

3.2.9. Active Serial Configuration Software Settings

3.2.10. Intel® Quartus® Prime Programming Steps

3.2.11. Debugging Guidelines for the AS Configuration Scheme

5.1. Remote System Update Functional Description

5.2. Guidelines for Performing Remote System Update Functions for Non-HPS

5.3. Commands and Responses

5.4. Quad SPI Flash Layout

5.5. Generating Remote System Update Image Files Using the Programming File Generator

5.6. Remote System Update from FPGA Core Example

5.6.1. Prerequisites

5.6.2. Creating Initial Flash Image Containing Bitstreams for Factory Image and One Application Image

5.6.3. Programming Flash Memory with the Initial Remote System Update Image

5.6.4. Reconfiguring the Device with an Application or Factory Image

5.6.5. Adding an Application Image

5.6.6. Removing an Application Image

7.1. Configuration Debugging Checklist

7.2. Intel® Stratix® 10 Configuration Architecture Overview

7.3. Understanding Configuration Status Using quartus_pgm command

7.4. SDM Debug Toolkit Overview

7.5. Configuration Pin Differences from Previous Device Families

7.6. Configuration File Format Differences

7.7. Understanding SEUs

7.8. Reading the Unique 64-Bit CHIP ID

7.9. E-Tile Transceivers May Fail To Configure

7.10. Understanding and Troubleshooting Configuration Pin Behavior

Visible to Intel only — GUID: sss1466499088458

Ixiasoft

3.2.10.1. Generating Programming Files using the Programming File Generator

By default, the Intel® Quartus® Prime Compiler's Assembler module generates the .sof file required for device programming at the end of full compilation. You can use the Programming File Generator to generate programming files for alternative device programming methods, such as the .jic for flash programming, or .rpd for third-party programmer configuration. The Programming File Generator supports Intel® Stratix® 10 and later devices. The legacy Convert Programming Files dialog box does not support some advanced programming features for Intel® Stratix® 10 and later devices.

Note: If you are generating an .rpd for remote system update (RSU), you must follow the instructions in Generating an Application Image in the Remote System Update chapter. This procedure generates flash programming files for Intel® Stratix® 10 devices.

View the video guide and complete the following steps to generate the programming file(s) you require:

- Click File > Programming File Generator .

- For Device Family select Intel® Stratix® 10

- In the Configuration mode, select Active Serial x4.

- Specify the Output directory and Name for the file you generate.

- Under Output directory, select the appropriate file type for your design. The AS scheme supports the Programmer Object File (.pof), JTAG Indirect Configuration File (.jic), and Raw Programming Data File (.rpd) file types.

Figure 48. Programming File Generator Output Files

- For the JTAG Indirect Configuration File (.jic) and Programmer Object File (.pof) you can turn on the Memory Map File (.map). This option describes flash memory address locations.

The Input Files tab is now available.

- On the Input Files tab, click Add Bitstream and browse to your configuration bitstream.

Figure 49. Programing File Generator Input Files

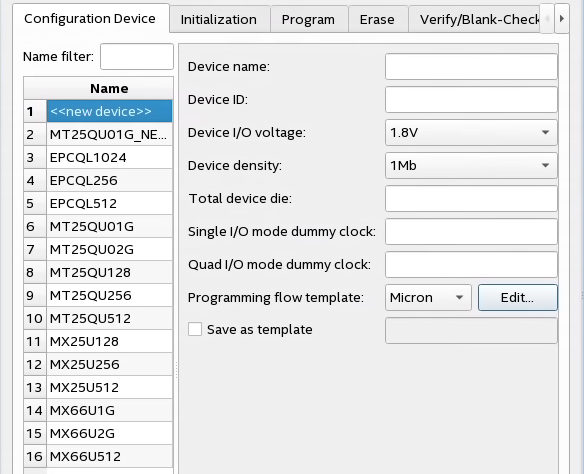

- On the Configuration Device tab, click Add Device. You can select your flash device from the Configuration Device list, or define a custom device using the available menu options. For more information about defining a custom configuration device, refer to the Configuration Device Tab Settings (Programming File Generator) in the Intel® Quartus® Prime Pro Edition User Guide: Programmer

Figure 50. Programming File Generator: Configuration Device Tab

Note: You do not need to specify the flash device for .rpd files because the .rpd format is independent of the flash device. In contrast, the .pof and .jic files include both programming data and additional data specific to the configuration device. The Intel® Quartus® Prime Programmer uses this additional data to establish communication with the configuration device and then write the programming data.

Note: You do not need to specify the flash device for .rpd files because the .rpd format is independent of the flash device. In contrast, the .pof and .jic files include both programming data and additional data specific to the configuration device. The Intel® Quartus® Prime Programmer uses this additional data to establish communication with the configuration device and then write the programming data. - Click Generate to generate the programming file(s).

- You can optionally Click File > Save As .. to save the configuration parameters as a file with the .pfg extension. The .pfg file contains your settings for the Programming File Generator. After you save the .pfg, you can use this file to regenerate the programming file by running the following command:

quartus_pfg -c <configuration_file>.pfg