Visible to Intel only — GUID: eis1411631443376

Ixiasoft

Visible to Intel only — GUID: eis1411631443376

Ixiasoft

14.4.1. ALTFP_COMPARE Design Example: Understanding the Simulation Results

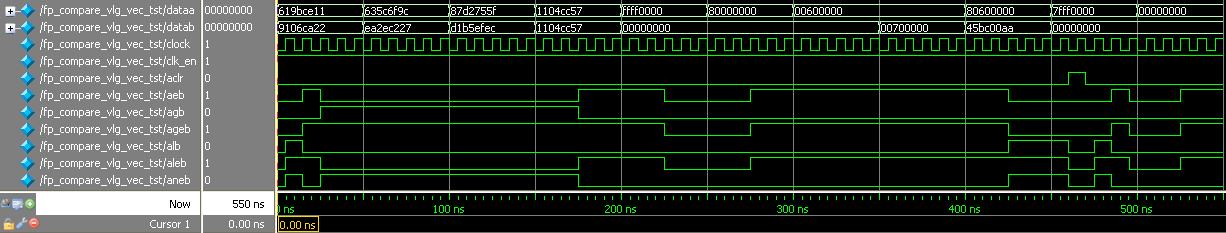

This figure shows the expected simulation results in the ModelSim* - Intel® FPGA Edition software.

This design example implements a floating-point comparator for single-precision numbers. Both optional input ports (clk_en and aclr) and all seven output ports (ageb, aeb, agb, aneb, alb, aleb, and unordered) are enabled.

The chosen output latency is 3. Therefore, the comparison operation generates the output result 3 clock cycles later.

This table lists the inputs and corresponding outputs obtained from the simulation in the waveform.

| Time | Event |

|---|---|

| 0 ns, start-up | dataa[] value: 619B CE11h datab[] value: 9106 CA22h Output value: An undefined value is seen on the result[] port, which is ignored. All values seen on the output port before the 3rd clock cycle are merely due to the behavior of the system during start-up and should be disregarded. |

| 25 ns | Output ports: ageb, aneb, and agb assert |

| 350 ns | dataa[] value: 0060 0000h datab[] value: 0070 0000h Both input values are denormal numbers. |

| 375 ns | Output ports: aeb, ageb, and aleb assert Denormal inputs are not supported and are forced to zero before comparison takes place, which results in the dataa[] value being equal to datab[]. |

| 460 ns | The aclr signal is set for 1 clock cycle. |

| 495.5 ns | The comparisons of subsequent data inputs are performed 3 clock cycles after the aclr signal deasserts. |