A newer version of this document is available. Customers should click here to go to the newest version.

Visible to Intel only — GUID: eis1411545767576

Ixiasoft

Visible to Intel only — GUID: eis1411545767576

Ixiasoft

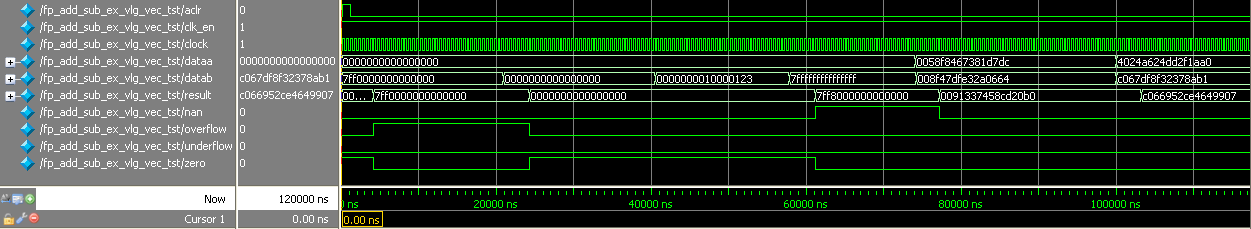

3.5.1. ALTFP_ADD_SUM Design Example: Understanding the Simulation Results

This design example implements a floating-point adder for the addition of double-precision format numbers. All the optional input ports (clk_en and aclr) and optional output ports (overflow, underflow, zero, and nan) are enabled.

In this example, the output latency of the multiplier is set to 7 clock cycles. Every addition result appears at the result[] port 7 clock cycles after the input values are captured on the dataa[] and datab[] ports.

The following lists the inputs and corresponding outputs obtained from the simulation waveform.

| Time | Event |

|---|---|

| 0 ns, start-up | dataa[] value: 0000 0000 0000 0000h datab[] value: 7FF0 0000 0000 0000h Output value: All values seen on the output port before the 7th clock cycle are merely due to the behavior of the system during startup and should be disregarded. |

| 4250 ns | Output value: 7FF0 0000 0000 0000h Exception handling ports: overflow asserts The addition of zero at the input port dataa[], and infinity value at the input port datab[] results in infinity value. |

| 40,511 ns | dataa[] value: 0000 0000 0000 0000h datab[] value: 0000 0000 1000 0123h The is the addition of a zero and a denormal value. |

| 43,750 ns | Output value: 0000 0000 0000 0000h Exception handling ports: zero remains asserted. Denormal inputs are not supported and are forced to zero before addition takes place.This results in a zero. |