AN 777: Data Word Alignment Calibration With Multiple Intel FPGA PHYLite for Parallel Interfaces IP Cores

1.8.3. Timing Analysis Guidelines

It is crucial to set the Input Strobe Setup Delay, Input Strobe Hold Delay Constraint, Output Strobe Setup Delay Constraint, and Output Strobe Hold Delay Constraint for both dut_INPUT and dut_OUTPUT module to 0 initially to eliminate unnecessary interface constraints. The phylite_interface_constraints.tcl script then automatically calculates the TcoMax and TcoMin values for input interface delay constraints and Tsu and Th values for output interface delay constraints.

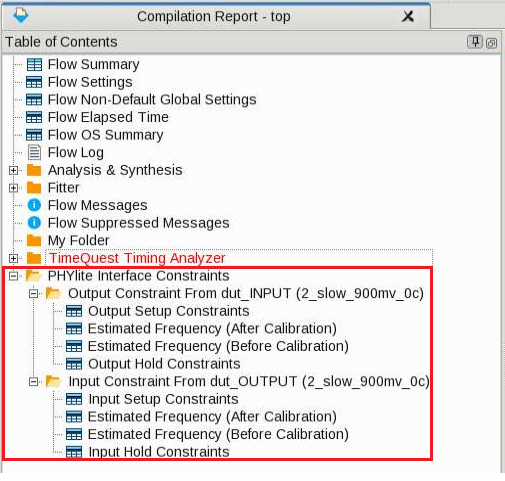

The TimeQuest Analyzer generates a report based on the calculations performed by the script.

Input Interface Delay Constraints

Use the TcoMax value to calculate the Input Strobe Setup Delay Constraint and TcoMin value to calculate the Input Strobe Hold Delay Constraint. The input interface delay constraints must include board skew to perform accurate timing analysis.

Input Strobe Setup Delay Constraint = TcoMax + board skew

Input Strobe Hold Delay Constraint = TcoMin + board skew

Update the new Input Strobe Setup Delay Constraint and Input Strobe Hold Delay Constraint values to the dut_INPUT module and re-compile the design.

Output Interface Delay Constraints

Use the Tsu value to calcuate the Output Strobe Setup Delay Constraint and Th value to calculate Output Strobe Hold Delay Constraint. The output interface delay constraints must include board skew to perform accurate timing analysis.

Output Strobe Setup Delay Constraint = Tsu + board skew

Output Strobe Hold Delay Constraint = Th - board skew

Update the new Output Strobe Setup Delay Constraint and Output Strobe Hold Delay Constraint values to the dut_OUTPUT module and re-compile the design.