AN 777: Data Word Alignment Calibration With Multiple Intel FPGA PHYLite for Parallel Interfaces IP Cores

1.8.2. Data Word Alignment Algorithm

Figure 15. Data Word Alignment Algorithm

The data word alignment algorithm starts by Nios II processor setting the strobe enable delay and read valid enable delay of the dut_INPUT to the minimum read latency based on the FPGA core clock rate and the VCO frequency multiplier factor.

Next, Nios II processor asserts oe_from_core signal to initiate data transmission to dut_OUTPUT and sends a set of test data to the dut_OUTPUT.

The dut_OUTPUT transmit the test data to the dut_INPUT. The rcfg_data_from_core signals show the data value transmitted from dut_OUTPUT.

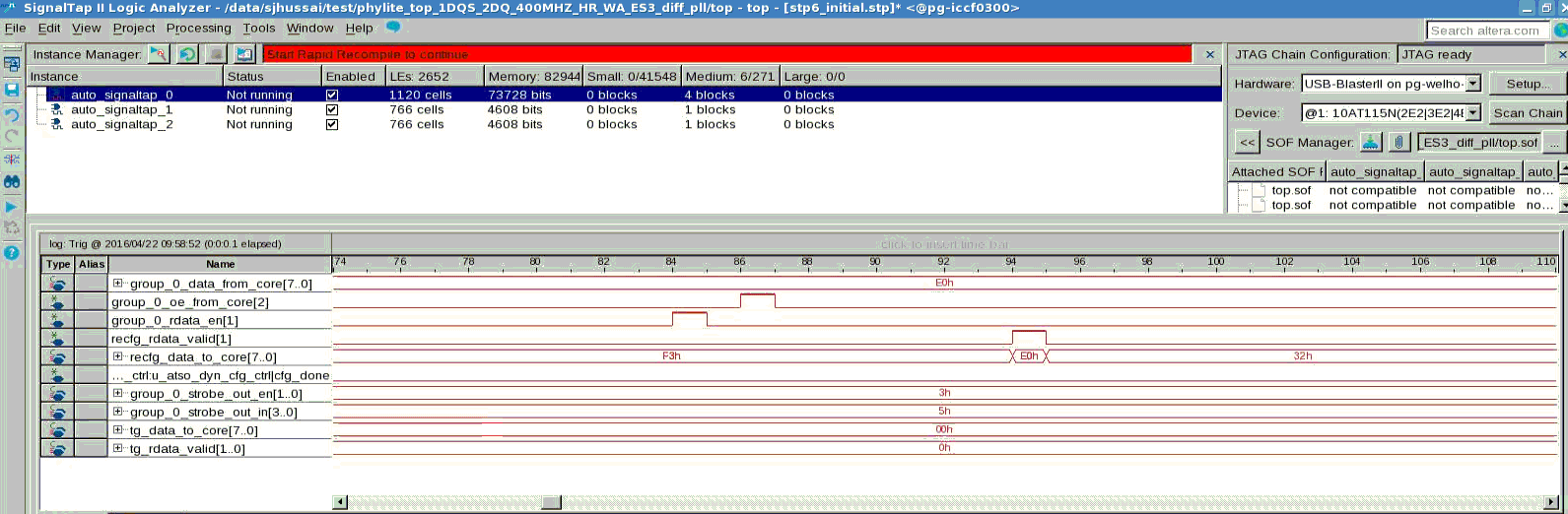

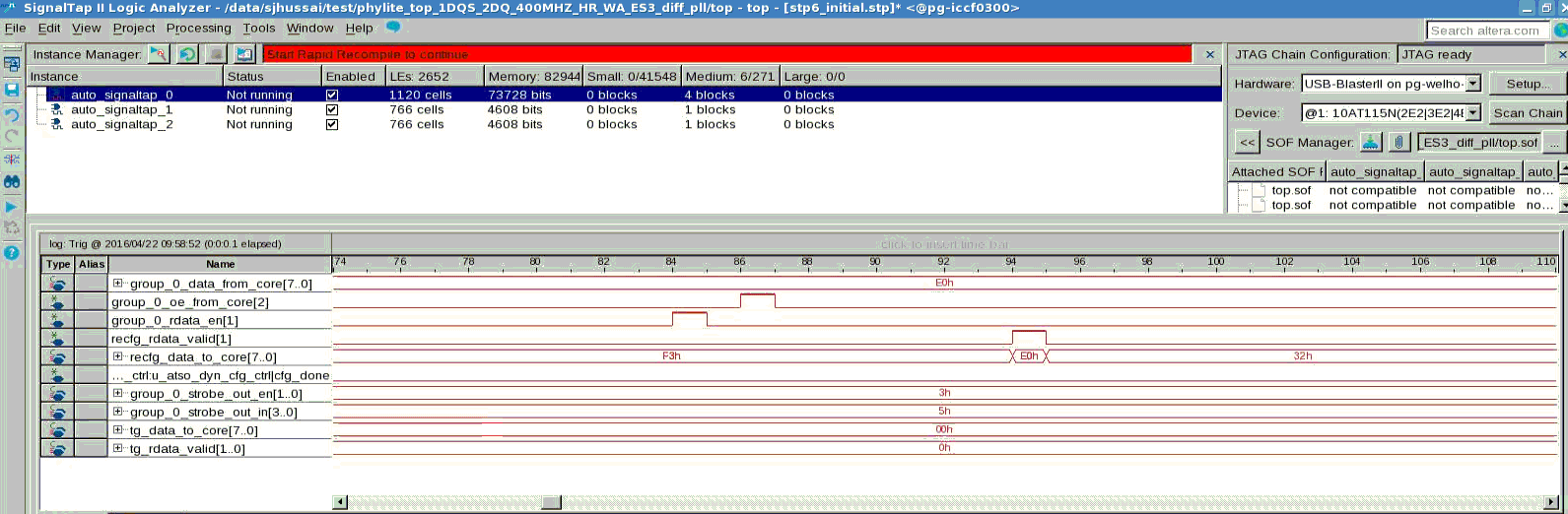

Next, the dut_INPUT sends the test data to Nios II processor for data verification. Nios II asserts recfg_rdata_en signal to dut_INPUT to capture the data transmitted from dut_OUTPUT. The dut_INPUT module asserts recfg_rdata_valid signal to indicates the received data in the dut_INPUT read FIFO is valid. If the received test data does not match the expected data, Nios II processor increases the strobe enable delay and read valid enable delay of the dut_INPUT module, and repeats the process of sending test data to dut_OUTPUT and verify the received data from dut_INPUT.

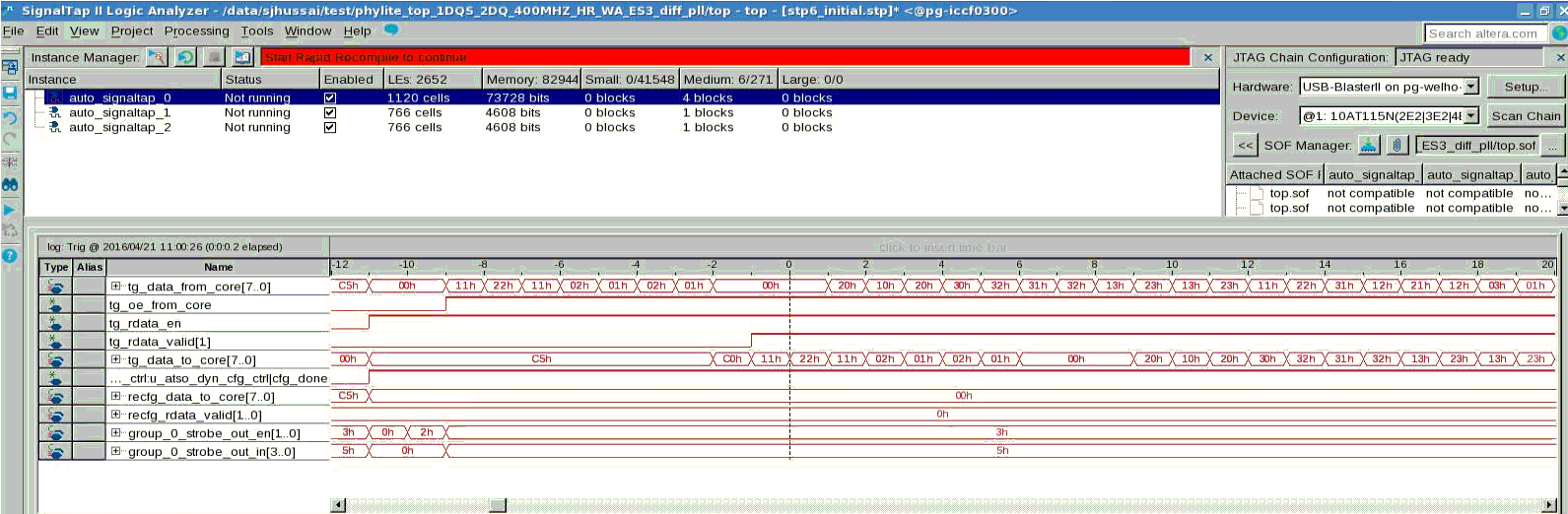

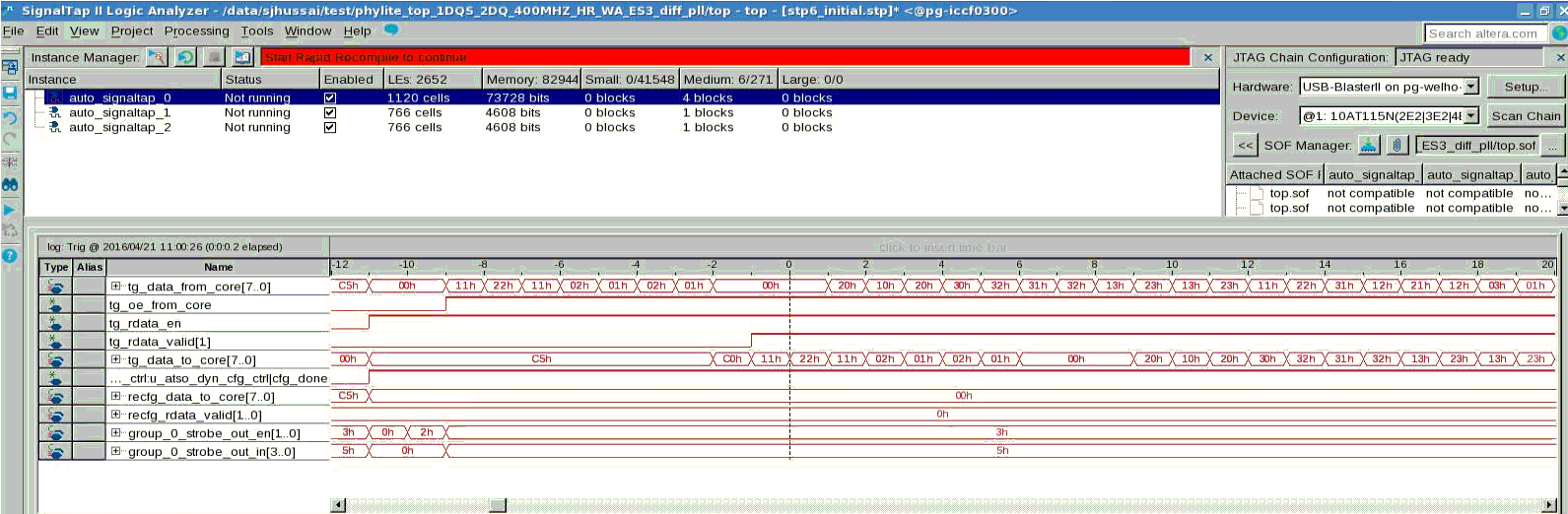

Figure 16. Signal Tap Waveform for Mismatch Data during Dynamic Reconfiguration

The algorithm stops when the received data matches the transmitted data or if the strobe enable delay and read valid enable delay reach the maximum values. Nios II asserts cfg_done signal to indicate reconfiguration completed and allow traffic generator to start sending data.

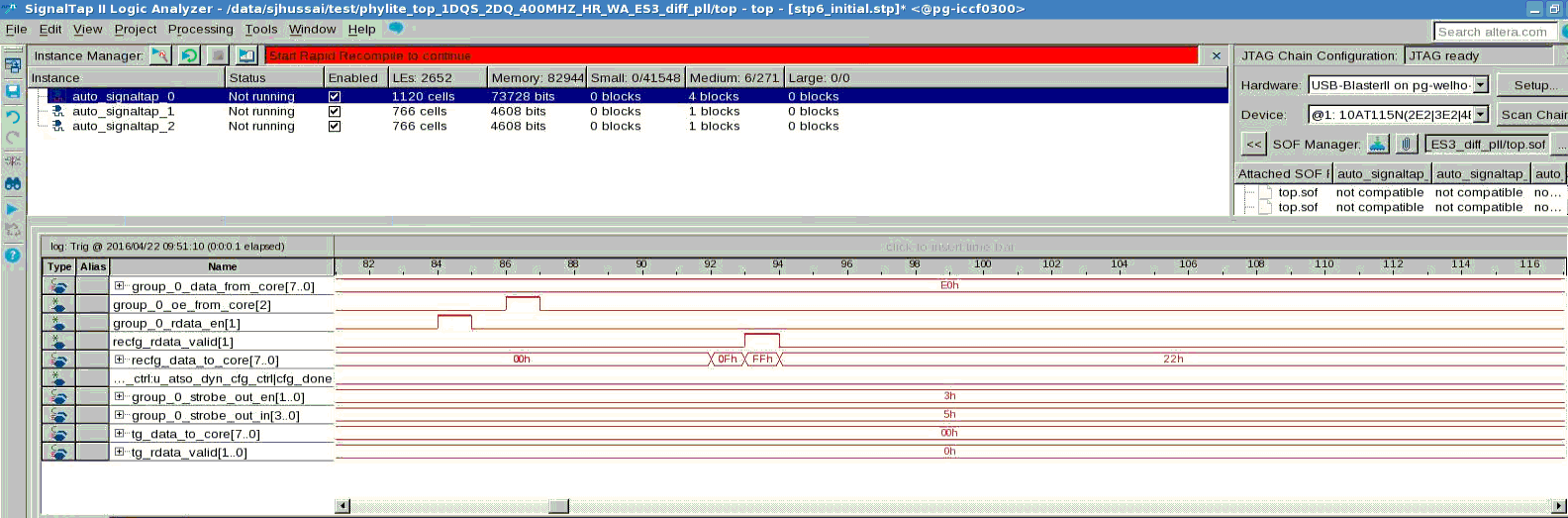

Figure 17. Signal Tap Waveform for Match Data during Dynamic Reconfiguration

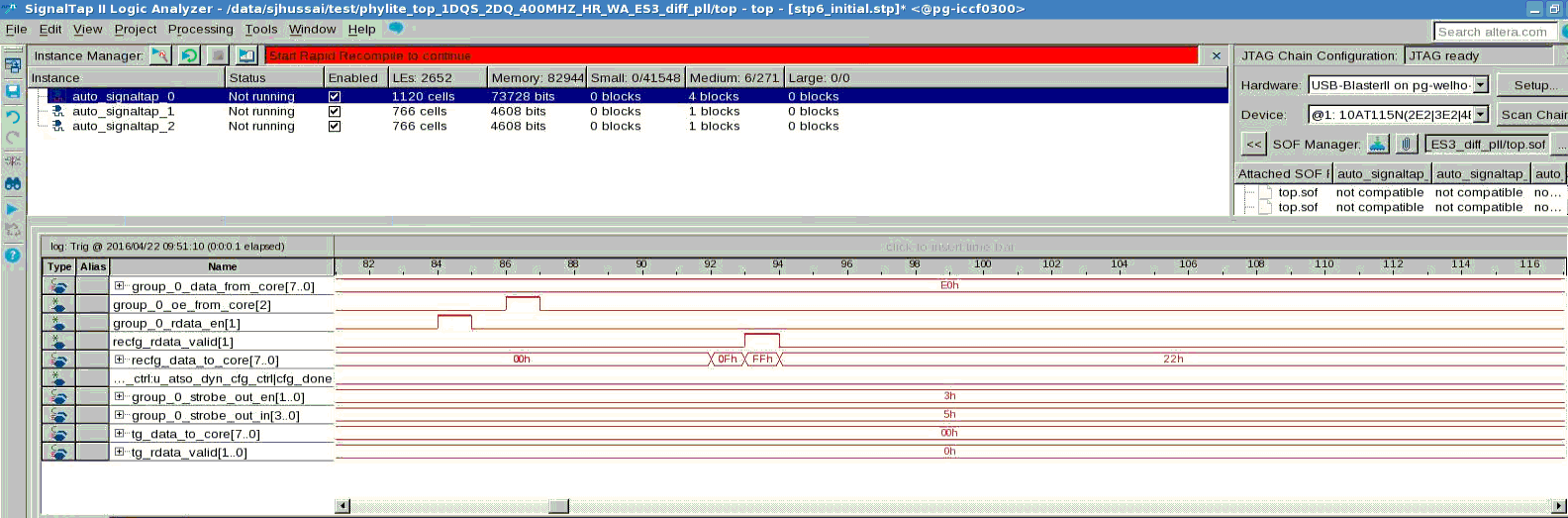

Figure 18. Signal Tap Waveform for Reconfiguration Complete