1.5.3. Steps for Auto Rate Negotiation

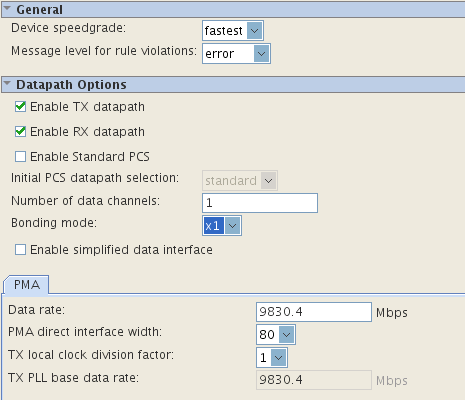

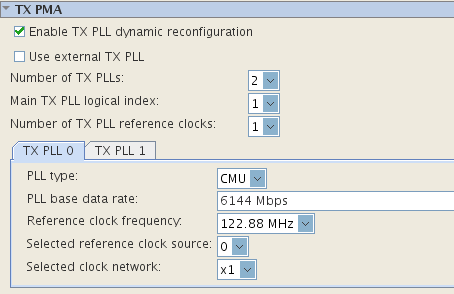

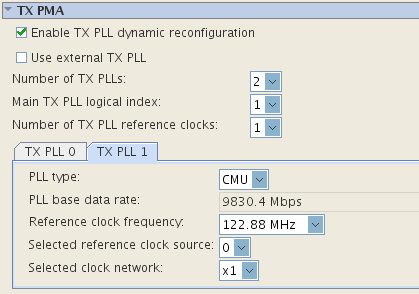

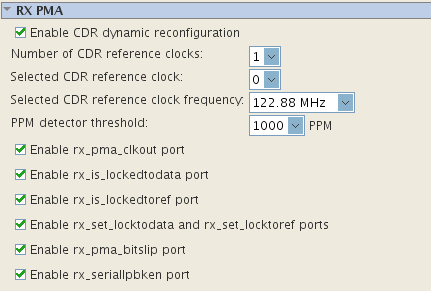

- Create the original design for the data rate of 9.8304 Gbps. Refer to the following figures for information about data path options, TX and RX PMA settings for the original design.

Figure 7. Datapath Options and PMA Settings

Figure 8. TX PLL 0 Settings

Figure 9. TX PLL 1 Settings

Figure 10. RX PMA Settings

Note: If Enable rx_pma_bitslip port option is turned on, the deserializer slips one clock edge each time this signal is asserted. This feature is used to reduce the uncertainty in the serialization process for the data path with deterministic latency. - Create 9.8304 Gbps, 6.144 Gbps, 4.9152 Gbps, 3.072 Gbps, 2.4576 Gbps and 1.2288 Gbps Memory Initialization File (MIF) design. The MIF design is the original design with different settings specified for Native PHY IP. In the original design, the initial data rate is 9.8304 Gbps.

- Refer to the table below for the Native PHY IP settings used to generate the appropriate MIF. The PHY IP settings not listed in the table below are same as the original design. Set PMA data rate to the desired data rate for the static design.

Table 3. Native PHY IP PMA Settings Data Rate for MIF (Gbps) PMA TX PMA TX PLL1 TX PLL0 Data Rate (Mbps) TX Local Clock Divider Factor TX PLL Base Data Rate (Mbps) Use External TX PLL Number of TX PLLs Main TX PLL Logical Index PLL Base Data Rate (Mbps) Selected Clock Network PLL Base Data Rate (Mbps) Selected Clock Network 9.8304 9830.4 1 9830.4 Disabled 2 1 9830.4 x1 6144 x1 6.144 6144 1 6144 Disabled 2 0 9830.4 x1 6144 x1 4.9152 4915.2 2 9830.4 Disabled 2 1 9830.4 x1 6144 x1 3.072 3072 2 6144 Disabled 2 0 9830.4 x1 6144 x1 2.4576 2457.6 4 9830.4 Disabled 2 1 9830.4 x1 6144 x1 1.2288 1228.8 8 9830.4 Disabled 2 1 9830.4 x1 6144 x1 - Connect the design as shown in Figure 4.

- For the original design running at the data rate of 9.8304 Gbps:

- Set usr_clk to 245.76 MHz and usr_pma_clk to 122.88 MHz.

- Set data_width_pma to 7’d80.

- Set TX PLL 1 base data rate to 9.8304 Gbps and TX PLL 0 base data rate to 6.144 Gbps.

- Follow the appropriate option from the list below to reconfigure to the required data rate.

Note:

- Refer to AN676 Using the Transceiver Reconfiguration Controller for Dynamic Reconfiguration in Arria V and Cyclone V Devices for information about the reset controller, CMU PLL, and the reconfiguration controller settings.

- Refer to AN 661 Implementing Fractional PLL Reconfiguration with ALTERA_PLL and ALTERA_PLL_RECONFIG Megafunctions for information about implementing fPLL reconfiguration.

- To reconfigure the data rate to 6.144 Gbps:

- Reconfigure fPLL

- Change usr_clk to 153.6 MHz.

- Change usr_pma_clk to 76.8 MHz.

- Use the 6.144 Gbps MIF to perform channel reconfiguration and TX PLL switching.

- Set data_width_pma to 7'd80.

- Reconfigure fPLL

- To reconfigure the data rate to 4.9512 Gbps:

- Reconfigure fPLL:

- Change usr_clk to 122.88 MHz.

- Change usr__pma_clk to 61.44 MHz.

- Use the 4.9152 Gbps MIF to perform channel reconfiguration and TX PLL switching.

- Set data_width_pma to 7'd80.

- Reconfigure fPLL:

- To reconfigure the data rate to 3.072 Gbps:

- Reconfigure fPLL:

- Change usr_clk to 76.8 MHz.

- Change usr_pma_clk to 153.6 MHz.

- Use the 3.072 Gbps MIF to perform channel reconfiguration and TX PLL switching.

- Set data_width_pma to 7'd20.

- Reconfigure fPLL:

- To reconfigure the data rate to 2.4576 Gbps:

- Reconfigure fPLL:

- Change usr_clk to 61.44 MHz.

- Change usr_pma_clk to 122.88 MHz.

- Use the 2.4576 Gbps MIF to perform channel reconfiguration and TX PLL switching.

- Set data_width_pma to 7'd20.

- Reconfigure fPLL:

- To reconfigure the data rate to 1.2288 Gbps:

- Reconfigure fPLL:

- Change usr_clk to 30.72 MHz.

- Change usr_pma_clk to 61.44 MHz.

- Use the 1.2288 Gbps MIF to perform channel reconfiguration and TX PLL switching.

- Set data_width_pma to 7'd20.

- Reconfigure fPLL: