AN 686: Implementing 9.8 Gbps CPRI in Arria V GT and ST Devices

Visible to Intel only — GUID: nik1412638552726

Ixiasoft

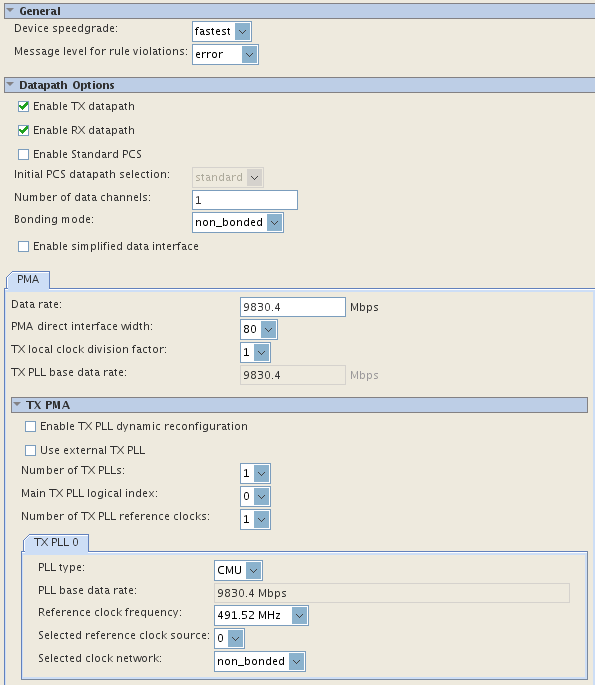

1.1. Native PHY IP Settings in PMA Direct Mode

The following figures show the Native PHY IP settings to implement a duplex transceiver channel in PMA direct mode. For this example, the reference clock frequency is set to 491.52 MHz. You can change the reference clock frequency using the drop down menu.

In this example, only one TX PLL is used to drive the channels.

The Native PHY IP does not include an embedded reset controller. You can either design custom reset logic or incorporate Altera’s “Transceiver PHY Reset Controller IP Core” to implement reset functionality.