Visible to Intel only — GUID: ycq1712091073941

Ixiasoft

1.2.1. Functional Description for the Programmed Input/Output (PIO) Design Example

1.2.2. Functional Description for the Single Root I/O Virtualization (SR-IOV) Design Example

1.2.3. Functional Description for the Performance Design Example

1.2.4. Functional Description for the Performance Design Example for TL Bypass Mode

1.2.5. Hardware and Software Requirements

2.4.5.1. ebfm_barwr Procedure

2.4.5.2. ebfm_barwr_imm Procedure

2.4.5.3. ebfm_barrd_wait Procedure

2.4.5.4. ebfm_barrd_nowt Procedure

2.4.5.5. ebfm_cfgwr_imm_wait Procedure

2.4.5.6. ebfm_cfgwr_imm_nowt Procedure

2.4.5.7. ebfm_cfgrd_wait Procedure

2.4.5.8. ebfm_cfgrd_nowt Procedure

2.4.5.9. BFM Configuration Procedures

2.4.5.10. BFM Shared Memory Access Procedures

2.4.5.11. BFM Log and Message Procedures

2.4.5.12. Verilog HDL Formatting Functions

2.4.5.11.1. ebfm_display Verilog HDL Function

2.4.5.11.2. ebfm_log_stop_sim Verilog HDL Function

2.4.5.11.3. ebfm_log_set_suppressed_msg_mask Task

2.4.5.11.4. ebfm_log_set_stop_on_msg_mask Verilog HDL Task

2.4.5.11.5. ebfm_log_open Verilog HDL Function

2.4.5.11.6. ebfm_log_close Verilog HDL Function

Visible to Intel only — GUID: ycq1712091073941

Ixiasoft

2.7.4. Running the Performance Design Example for TL Bypass Mode

To run the Performance Design Example for TL Bypass mode, repeat steps 1 to 5 from section Running the Performance Design Example (Endpoint) and continue with the steps below.

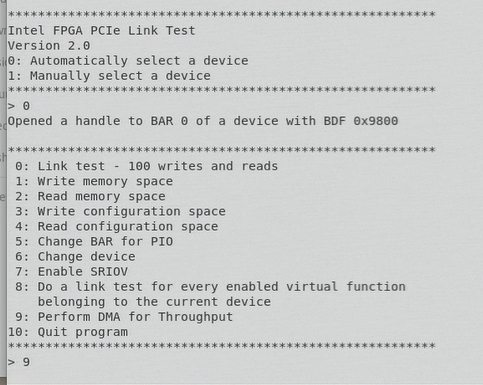

- The Performance Design Example for TL Bypass mode for the R-Tile Avalon Streaming Intel FPGA IP only supports menu option 9. Enter 9 and press Enter to proceed.

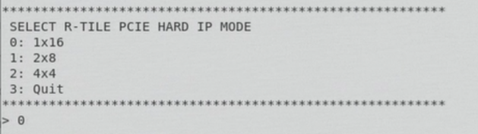

- Select the R-Tile PCIe Hard IP mode.

Note: For the Performance Design Example for TL Bypass mode, only the 1x16 R-Tile PCIe Hard IP Mode is supported in the current release of the Quartus® Prime software.

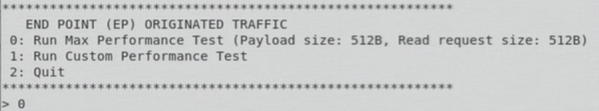

- Select the End Point Originated Traffic. For the Performance Design Example for TL Bypass mode with 1x16 R-Tile PCIe Hard IP Mode, you are allowed to run the Max Performance Test or Custom Performance Test.

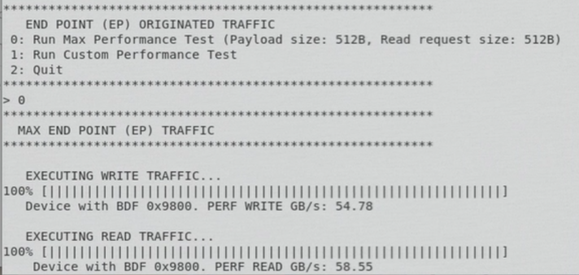

- The option 0: Run Max Performance Test generates Memory Write traffic, Memory Read traffic and simultaneous Memory Write and Memory Read Traffic with the payload size and read request size that allow you to obtain the maximum performance.

- The option 1: Run Custom Performance Test allows you to configure the traffic sent during the performance test. By selecting this option, you are able to enter the number of iterations to be carried out, the Payload Size for Memory transactions, the Read Request Size for Memory Read transactions, as well as the type of traffic to execute.