Visible to Intel only — GUID: xtn1614202226235

Ixiasoft

1.2.1. Functional Description for the Programmed Input/Output (PIO) Design Example

1.2.2. Functional Description for the Single Root I/O Virtualization (SR-IOV) Design Example

1.2.3. Functional Description for the Performance Design Example

1.2.4. Functional Description for the Performance Design Example for TL Bypass Mode

1.2.5. Hardware and Software Requirements

2.4.5.1. ebfm_barwr Procedure

2.4.5.2. ebfm_barwr_imm Procedure

2.4.5.3. ebfm_barrd_wait Procedure

2.4.5.4. ebfm_barrd_nowt Procedure

2.4.5.5. ebfm_cfgwr_imm_wait Procedure

2.4.5.6. ebfm_cfgwr_imm_nowt Procedure

2.4.5.7. ebfm_cfgrd_wait Procedure

2.4.5.8. ebfm_cfgrd_nowt Procedure

2.4.5.9. BFM Configuration Procedures

2.4.5.10. BFM Shared Memory Access Procedures

2.4.5.11. BFM Log and Message Procedures

2.4.5.12. Verilog HDL Formatting Functions

2.4.5.11.1. ebfm_display Verilog HDL Function

2.4.5.11.2. ebfm_log_stop_sim Verilog HDL Function

2.4.5.11.3. ebfm_log_set_suppressed_msg_mask Task

2.4.5.11.4. ebfm_log_set_stop_on_msg_mask Verilog HDL Task

2.4.5.11.5. ebfm_log_open Verilog HDL Function

2.4.5.11.6. ebfm_log_close Verilog HDL Function

Visible to Intel only — GUID: xtn1614202226235

Ixiasoft

2.2. Generating the Design Example

Figure 18. Procedure

- In the Quartus® Prime Pro Edition software, create a new project (File > New Project Wizard).

- Specify the Directory, Name, and Top-Level Entity.

- For Project Type, accept the default value, Empty project. Click Next.

- For Add Files click Next.

- For Family, Device & Board Settings under Family, select Agilex™ 7 I-Series.

- Select the Target Device for your design.

- Click Finish.

- In the IP Catalog locate and add the Intel R-Tile Avalon® -ST Hard IP for PCI Express* .

- In the New IP Variant dialog box, specify a name for your IP. Click Create.

- On the Top-Level Settings and PCIe* Settings tabs, specify the parameters for your IP variation.

If you want to run PIPE Mode simulations, enable the Enable PIPE Mode Simulation parameter in the Top-Level Settings tab. For more details on PIPE Mode simulations, refer to Generating the Design Example with R-Tile Configured in PIPE Mode.If you want to generate the SR-IOV design example, perform the following steps to enable SR-IOV:

- On the Top-Level Settings tab, set the PCIe Hard IP Mode parameter to Gen5 1x16, interface - 1024 bit

- On the PCIe0 Settings tab, navigate to PCIe0 PCI Express/PCI Capabilities > PCIe0 Device > PCIe0 Multifunction and SR-IOV System Settings and:

- Check the Enable Multiple Physical Functions parameter.

- Set the Total Physical Functions (PFs) parameter to 2.

- Check the Enable SR-IOV Support parameter.

- Set the Total Virtual Functions of Physical Function 0 (PF0 VFs) parameter to 32.

- Set the Total Virtual Functions of Physical Function 1 (PF1 VFs) parameter to 32.

- On the PCIe0 Settings tab, navigate to PCIe0 Base Address Registers > PCIe0 PF0 BAR Configuration > PCIe0 PF0 BAR and:

- Set the BAR0 Type parameter to 64-bit prefetchable memory or 64-bit non-prefetchable memory or 32-bit non-prefetchable memory.

- Set the BAR0 Size parameter to any value other than N/A.

- Repeat steps i and ii for PCIe0 PF0 BAR above in the PCIe0 PF0 VF BAR section.

- On the PCIe0 Settings tab, navigate to PCIe0 Base Address Registers > PCIe0 PF1 BAR Configuration > PCIe0 PF1 BAR and:

- Set the BAR0 Type parameter to 64-bit prefetchable memory or 64-bit non-prefetchable memory or 32-bit non-prefetchable memory.

- Set the BAR0 Size parameter to any value other than N/A.

- Repeat steps i and ii for PCIe0 PF1 BAR above in the PCIe0 PF1 VF BAR section.

- On the PCIe0 Settings tab, navigate to PCIe0 PCI Express/PCI Capabilities > PCIe0 MSI-X > PCIe0 PF MSI-X > PCIe0 PF0 MSI-X and check the Enable MSI-X parameter.

- On the PCIe0 Settings tab, navigate to PCIe0 PCI Express/PCI Capabilities > PCIe0 MSI-X > PCIe0 PF MSI-X > PCIe0 PF1 MSI-X and check the Enable MSI-X parameter.

- On the PCIe0 Settings tab, navigate to PCIe0 Device Identification Registers and set the following parameters for the PCIe0 PF0 IDs and the PCIe0 PF1 IDs:

- Vendor ID: 0x00001172

- Device ID: 0x00000000

- Revision ID: 0x00000001

- Class Code: 0x00ff0000

- Subsystem Vendor ID: 0x00001172

- Subsystem Device ID: 0x00000000

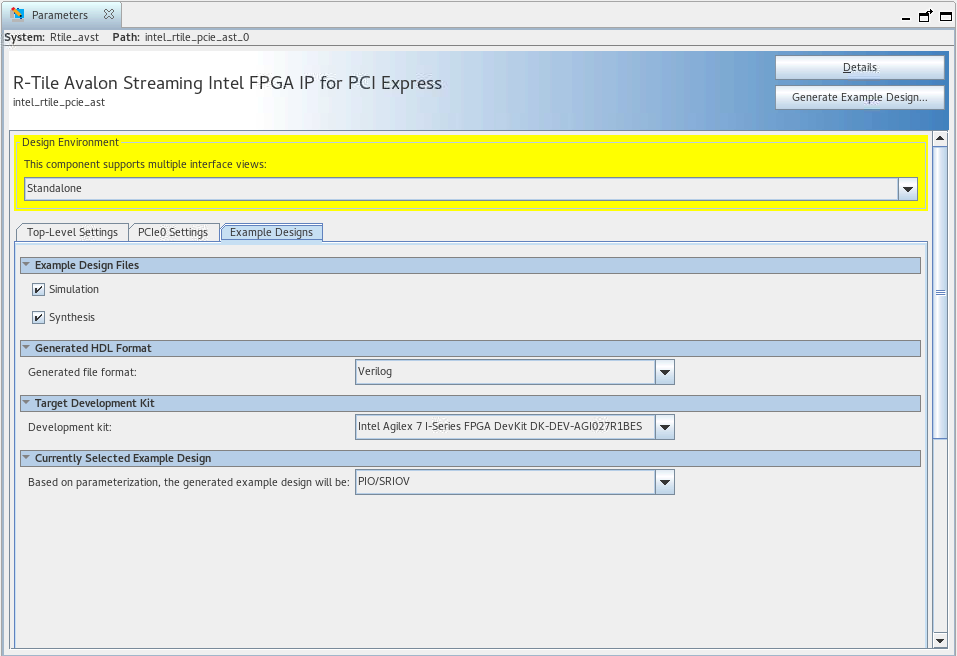

- On the Currently Selected Design Example tab, make the following selections:

- For Currently Selected Design Example select the PIO, SR-IOV or Performance design example.

- For Example Design Files, turn on the Simulation and Synthesis options. If you do not need these simulation or synthesis files, leaving the corresponding option(s) turned off significantly reduces the example design generation time.

- For Generated HDL Format, only Verilog is available in the current release.

- For Target Development Kit, select the appropriate development kit.

Note: If you select None, the generated design example targets the device you specified in Step 5 above. If you intend to test the design in hardware, make the appropriate pin assignments in the .qsf file. You can also use the pin planner tool to make pin assignments.Note: If you select a development kit, the device on that board overwrites the device selected in the Quartus® Prime project if the devices are different.Note: For Currently Selected Example Design, select PIO/SRIOV or PERFORMANCE_DESIGN.

- Select Generate Example Design to create a design example that you can simulate and download to hardware. If you select one of the R-Tile development boards, the device on that board overwrites the device previously selected in the Quartus® Prime project if the devices are different. When the prompt asks you to specify the directory for your example design, you can accept the default directory, ./intel_rtile_pcie_ast_0_example_design, or choose another directory.

Figure 19. IP Parameter Editor Screen for Generating Example Design

- Click Finish. You may save your .ip file when prompted, but it is not required to be able to use the example design.

- Close the current open project.

- Open the example design project. This is the new project that has been generated in the location specified in step 12.

- Compile the example design project to generate the .sof file for the complete example design.

- Close your example design project.

Note that you cannot change the PCIe pin allocations in the Quartus® Prime project. However, to ease PCB routing, you can take advantage of the lane reversal and polarity inversion features supported by this IP.