Visible to Intel only — GUID: prr1651627043921

Ixiasoft

1.2.1. Functional Description for the Programmed Input/Output (PIO) Design Example

1.2.2. Functional Description for the Single Root I/O Virtualization (SR-IOV) Design Example

1.2.3. Functional Description for the Performance Design Example

1.2.4. Functional Description for the Performance Design Example for TL Bypass Mode

1.2.5. Hardware and Software Requirements

2.4.5.1. ebfm_barwr Procedure

2.4.5.2. ebfm_barwr_imm Procedure

2.4.5.3. ebfm_barrd_wait Procedure

2.4.5.4. ebfm_barrd_nowt Procedure

2.4.5.5. ebfm_cfgwr_imm_wait Procedure

2.4.5.6. ebfm_cfgwr_imm_nowt Procedure

2.4.5.7. ebfm_cfgrd_wait Procedure

2.4.5.8. ebfm_cfgrd_nowt Procedure

2.4.5.9. BFM Configuration Procedures

2.4.5.10. BFM Shared Memory Access Procedures

2.4.5.11. BFM Log and Message Procedures

2.4.5.12. Verilog HDL Formatting Functions

2.4.5.11.1. ebfm_display Verilog HDL Function

2.4.5.11.2. ebfm_log_stop_sim Verilog HDL Function

2.4.5.11.3. ebfm_log_set_suppressed_msg_mask Task

2.4.5.11.4. ebfm_log_set_stop_on_msg_mask Verilog HDL Task

2.4.5.11.5. ebfm_log_open Verilog HDL Function

2.4.5.11.6. ebfm_log_close Verilog HDL Function

Visible to Intel only — GUID: prr1651627043921

Ixiasoft

2.3.1.4. Xcelium* Simulator

Note: Xcelium* simulator support is only available in devices with the following OPN numbers:

- AGIx027R29AxxxxR3

- AGIx027R29AxxxxR2

- AGIx027R29BxxxxR3

- AGIx023R18AxxxxR0

- AGIx041R29DxxxxR0

- AGIx041R29DxxxxR1

- AGMx039R47AxxR0

Perform the following steps to execute the simulation via a command line:

- Export the following environment variables:

- export CADENCE_ENABLE_AVSREQ_6614_PHASE_1=1

- export CADENCE_ENABLE_AVSREQ_12055_PHASE_1=1

- Change to the simulation working directory: cd <my_design>/pcie_ed_tb/pcie_ed_tb/sim/xcelium

- Execute the following command: sh xcelium_setup.sh USER_DEFINED_VERILOG_COMPILE_OPTIONS="-sv\ " USER_DEFINED_ELAB_OPTIONS="-timescale\ 1ns/1ps" USER_DEFINED_SIM_OPTIONS="-input\ @run" TOP_LEVEL_NAME="pcie_ed_tb.pcie_ed_tb" | tee simulation.log

Note: The command above is a single-line command.

Note: If R-Tile is configured with Enable PIPE Mode Simulation active, use the following command instead:

sh xcelium_setup.sh USER_DEFINED_VERILOG_COMPILE_OPTIONS="-sv\ +define+XTOR_PICECXL_LM_SVS_SERDES_ARCHITECTURE\ +define+RTILE_PIPE_MODE\ " USER_DEFINED_ELAB_OPTIONS="-timescale\ 1n/1ps" USER_DEFINED_SIM_OPTIONS="-input\ @run" TOP_LEVEL_NAME="pcie_ed_tb.pcie_ed_tb" | tee simulation.log

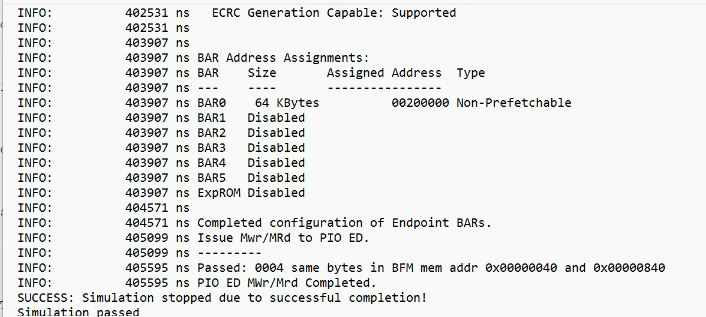

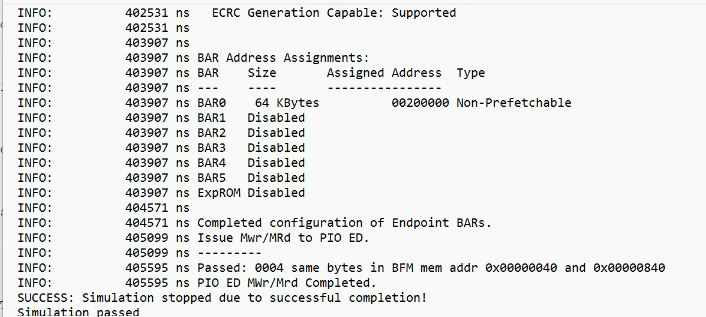

A successful simulation includes the following message: "Simulation stopped due to successful completion!"

Figure 26. Successful Simulation Message