Visible to Intel only — GUID: lyw1675893951461

Ixiasoft

1.2.1. Functional Description for the Programmed Input/Output (PIO) Design Example

1.2.2. Functional Description for the Single Root I/O Virtualization (SR-IOV) Design Example

1.2.3. Functional Description for the Performance Design Example

1.2.4. Functional Description for the Performance Design Example for TL Bypass Mode

1.2.5. Hardware and Software Requirements

2.4.5.1. ebfm_barwr Procedure

2.4.5.2. ebfm_barwr_imm Procedure

2.4.5.3. ebfm_barrd_wait Procedure

2.4.5.4. ebfm_barrd_nowt Procedure

2.4.5.5. ebfm_cfgwr_imm_wait Procedure

2.4.5.6. ebfm_cfgwr_imm_nowt Procedure

2.4.5.7. ebfm_cfgrd_wait Procedure

2.4.5.8. ebfm_cfgrd_nowt Procedure

2.4.5.9. BFM Configuration Procedures

2.4.5.10. BFM Shared Memory Access Procedures

2.4.5.11. BFM Log and Message Procedures

2.4.5.12. Verilog HDL Formatting Functions

2.4.5.11.1. ebfm_display Verilog HDL Function

2.4.5.11.2. ebfm_log_stop_sim Verilog HDL Function

2.4.5.11.3. ebfm_log_set_suppressed_msg_mask Task

2.4.5.11.4. ebfm_log_set_stop_on_msg_mask Verilog HDL Task

2.4.5.11.5. ebfm_log_open Verilog HDL Function

2.4.5.11.6. ebfm_log_close Verilog HDL Function

Visible to Intel only — GUID: lyw1675893951461

Ixiasoft

2.7.3. Running the Performance Design Example (Endpoint)

- Navigate to ./software/user/example under the design example directory.

- Compile the design example application:

$ sudo make

- Run the test:

$ sudo ./intel_fpga_pcie_link_test

You can run the Intel FPGA IP PCIe link test in manual or automatic mode. Choose from:- In automatic mode, the application automatically selects the device. The test selects the Intel PCIe device with the lowest BDF by matching the Vendor ID. The test also selects the lowest available BAR.

- In manual mode, the test queries you for the bus, device, and function numbers and BAR.

- For the Agilex™ 7 Development Kit, you can determine the BDF by typing the following command:

$ lspci -d 1172:

Note: This step is required if you run the Performance design example 2x8 or the Performance design example 4x4, in order to get the BDF numbers of the different ports. - Here is a sample transcript for the selection between automatic and manual modes:

# ./intel_fpga_pcie_link_test ********************************************************* Intel FPGA PCIe Link Test Version 2.0 0: Automatically select a device 1: Manually select a device *********************************************************

- The Performance design example for the Intel FPGA IP R-Tile Avalon Streaming Hard IP for PCI Express IP core only supports menu option 9. Enter 9 and press Enter to proceed.

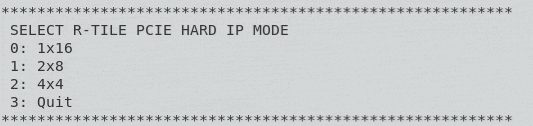

Opened a handle to BAR 0 of a device with BDF 0x3800 ********************************************************* 0: Link test - 100 writes and reads 1: Write memory space 2: Read memory space 3: Write configuration space 4: Read configuration space 5: Change BAR for PIO 6: Change device 7: Enable SRIOV 8: Do a link test for every enabled virtual function belonging to the current device 9: Perform DMA for Throughput 10: Quit program ********************************************************* > 9 - Select the R-Tile PCIe Hard IP mode.

- In case you select the 2x8 or 4x4 mode, the following menu is displayed, where you need to insert the BDF of each port, previously obtained in Step 4.

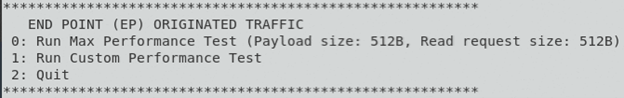

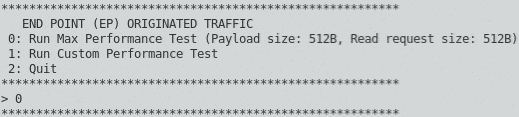

- All modes allow you to run the Max Performance Test or Custom Performance Test.

- The option 0: Run Max Performance Test generates Memory Write traffic, Memory Read traffic and simultaneous Memory Write and Memory Read Traffic with the payload size and read request size that allow you to obtain the maximum performance.

- Example of running Max Performance Test in the R-Tile PCIe Hard IP mode 1x16:

******************************************************************** MAX END POINT (EP) TRAFFIC ******************************************************************** EXECUTING WRITE TRAFFIC... 100% [||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||] PERF WRITE GB/s: 59.9366 EXECUTING READ TRAFFIC... 100% [||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||] PERF READ GB/s: 59.0977 - Example of running Max Performance Test in the R-Tile PCIe Hard IP mode 2x8:

******************************************************************** MAX END POINT (EP) TRAFFIC ******************************************************************** EXECUTING WRITE TRAFFIC... 100% [||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||] Device with BDF 0x3800. PERF WRITE GB/s: 29.95 Device with BDF 0x3900. PERF WRITE GB/s: 29.95 EXECUTING READ TRAFFIC... 100% [||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||] Device with BDF 0x3800. PERF READ GB/s: 29.19 Device with BDF 0x3900. PERF READ GB/s: 29.28 - Example of running Max Performance Test in the R-Tile PCIe Hard IP mode 4x4:

******************************************************************** MAX END POINT (EP) TRAFFIC ******************************************************************** EXECUTING WRITE TRAFFIC... 100% [||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||] Device with BDF 0x3300. PERF WRITE GB/s: 14.93 Device with BDF 0x3400. PERF WRITE GB/s: 14.93 Device with BDF 0x3500. PERF WRITE GB/s: 14.93 Device with BDF 0x3600. PERF WRITE GB/s: 14.93 EXECUTING READ TRAFFIC... 100% [||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||] Device with BDF 0x3300. PERF READ GB/s: 13.59 Device with BDF 0x3400. PERF READ GB/s: 13.59 Device with BDF 0x3500. PERF READ GB/s: 13.59 Device with BDF 0x3600. PERF READ GB/s: 13.59 ********************************************************************

- Example of running Max Performance Test in the R-Tile PCIe Hard IP mode 1x16:

- The option 1: Run Custom Performance Test allows you to configure the traffic sent during the performance test. By selecting this option, you are able to enter the number of iterations to be carried out, the Payload size for Memory transactions, the Read Request Size for Memory Read transactions, as well as the type of traffic to execute. In case you select the 2x8 or 4x4 mode, the settings for each port are required. If the numbers of loops differ between ports, the value provided in the second port is used.