Visible to Intel only — GUID: zps1596237359931

Ixiasoft

2.4.1.1. Simulation Results

Note: For detailed description about the testbench for this design example, refer to Example Testbench Flow for DMA Test with Avalon-ST Packet Generate/Check Design Example.

Figure 11. H2D Simulation Log

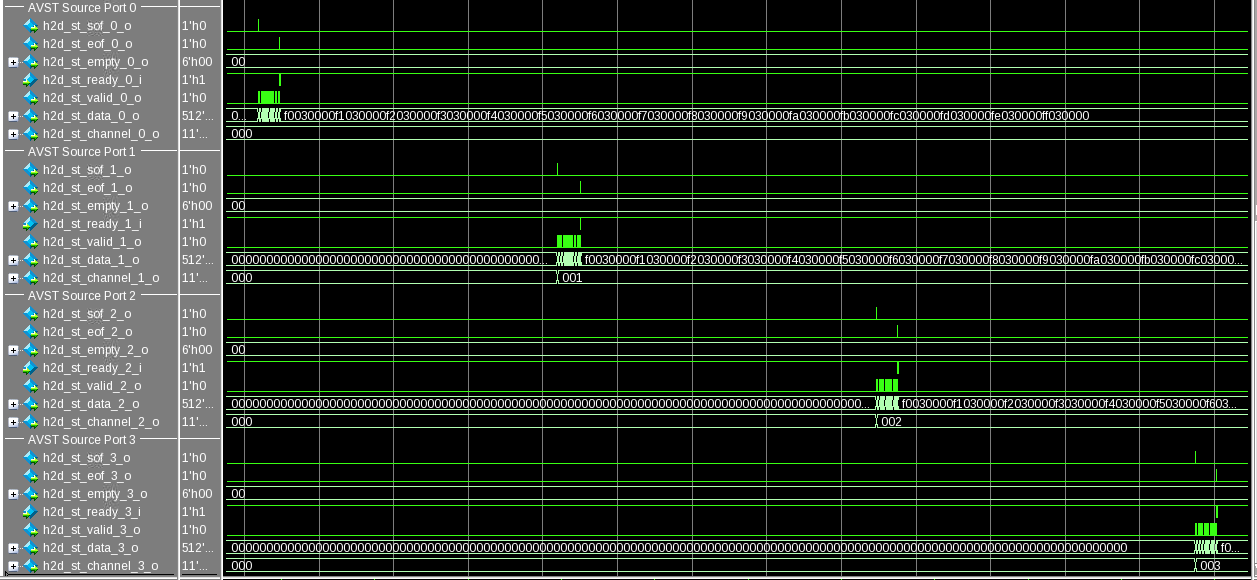

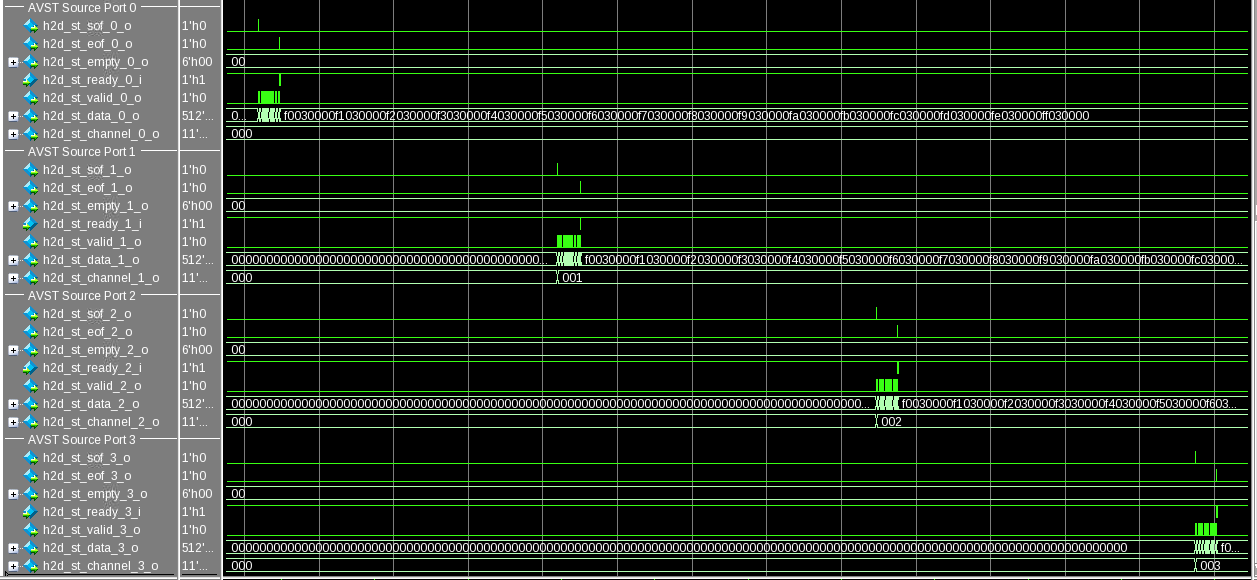

Figure 12. H2D Simulation Waveform

Figure 13. D2H Simulation Log

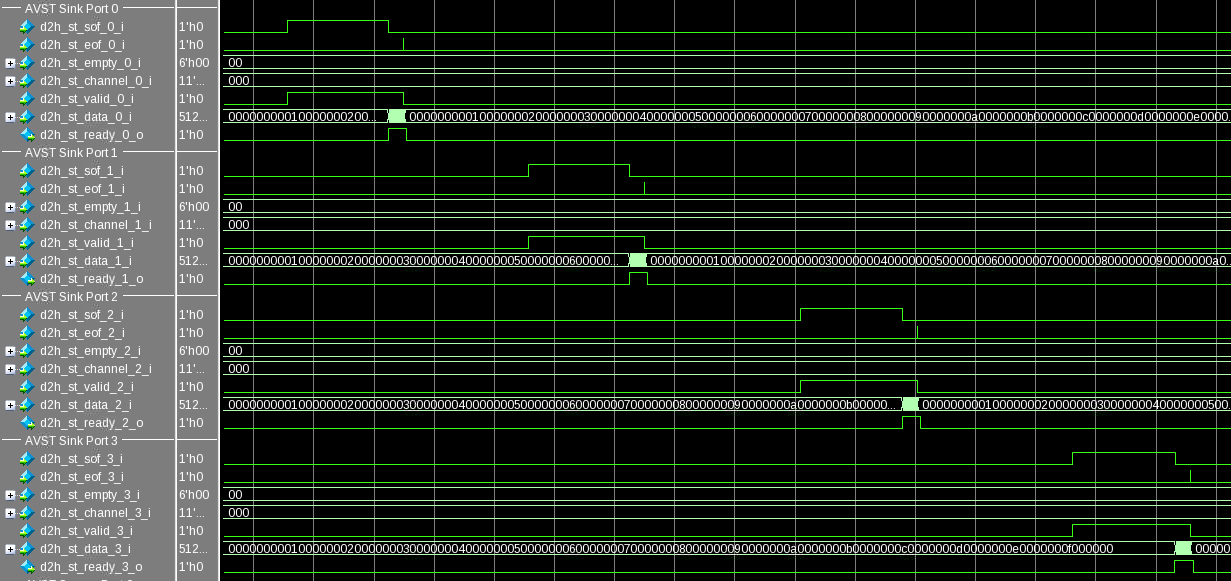

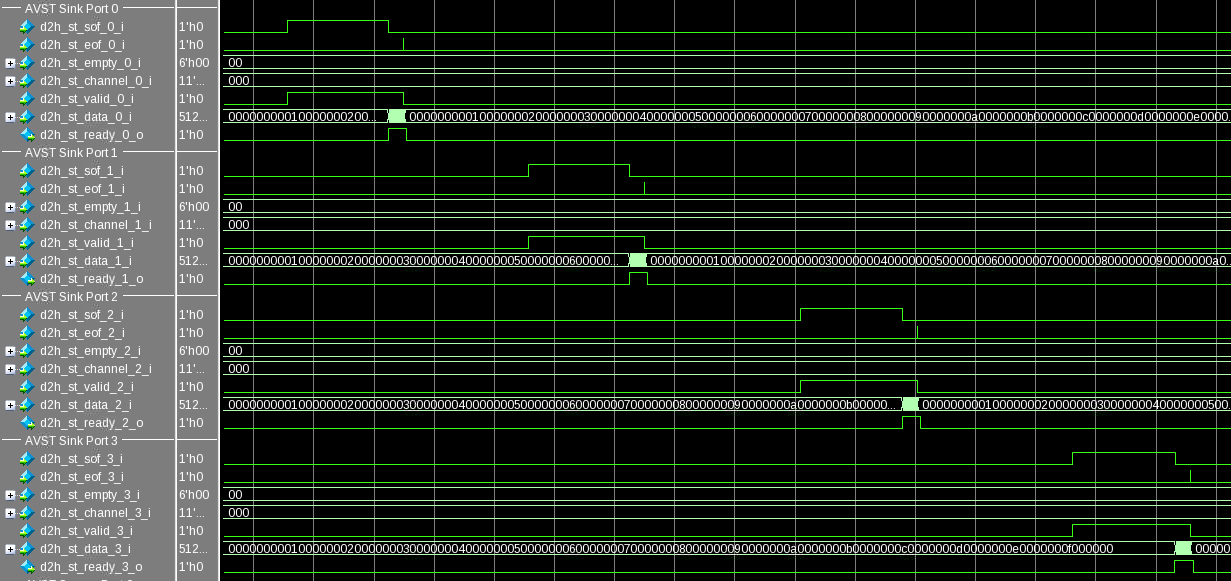

Figure 14. D2H Simulation Waveform