Visible to Intel only — GUID: lbx1666103856259

Ixiasoft

Answers to Top FAQs

1. Introduction to Quartus® Prime Pro Edition

2. Quick Start Steps

3. Planning FPGA Design for RTL Flow

4. Working With Intel® FPGA IP Cores

5. Creating a New FPGA Design Project

6. Migrate Your FPGA Design Project

7. Managing Quartus® Prime Projects

8. Next Steps After Getting Started

A. Using the Design Space Explorer II

B. Document Revision History for Quartus® Prime Pro Edition User Guide Getting Started

4.1. IP Catalog and Parameter Editor

4.2. Installing and Licensing Intel® FPGA IP Cores

4.3. IP General Settings

4.4. Adding IP to IP Catalog

4.5. Best Practices for Intel® FPGA IP

4.6. Specifying the IP Parameters and Options ( Quartus® Prime Pro Edition)

4.7. IP Core Generation Output ( Quartus® Prime Pro Edition)

4.8. Scripting IP Core Generation

4.9. Modifying an IP Variation

4.10. Upgrading IP Cores

4.11. Simulating Intel® FPGA IP Cores

4.12. Generating Simulation Files for Platform Designer Systems and IP Variants

4.13. Synthesizing IP Cores in Other EDA Tools

4.14. Instantiating IP Cores in HDL

4.15. Support for the IEEE 1735 Encryption Standard

4.16. Related Trainings and Resources

6.1.2.1. Modifying Entity Name Assignments

6.1.2.2. Resolving Timing Constraint Entity Names

6.1.2.3. Verifying Generated Node Name Assignments

6.1.2.4. Replace Logic Lock (Standard) Regions

6.1.2.5. Modifying Signal Tap Logic Analyzer Files

6.1.2.6. Removing References to .qip Files

6.1.2.7. Removing Unsupported Feature Assignments

6.1.4.1. Verifying Verilog Compilation Unit

6.1.4.2. Updating Entity Auto-Discovery

6.1.4.3. Ensuring Distinct VHDL Namespace for Each Library

6.1.4.4. Removing Unsupported Parameter Passing

6.1.4.5. Removing Unsized Constant from WYSIWYG Instantiation

6.1.4.6. Removing Non-Standard Pragmas

6.1.4.7. Declaring Objects Before Initial Values

6.1.4.8. Confining SystemVerilog Features to SystemVerilog Files

6.1.4.9. Avoiding Assignment Mixing in Always Blocks

6.1.4.10. Avoiding Unconnected, Non-Existent Ports

6.1.4.11. Avoiding Invalid Parameter Ranges

6.1.4.12. Updating Verilog HDL and VHDL Type Mapping

6.1.4.13. Converting Symbolic BDF Files to Acceptable File Formats

7.1. Viewing Basic Project Information

7.2. Managing Project Settings

7.3. Viewing Parameter Settings From the Project Navigator

7.4. Managing Logic Design Files

7.5. Managing Timing Constraints

7.6. Integrating Other EDA Tools

7.7. Exporting Compilation Results

7.8. Archiving Projects

7.9. Command-Line Interface

7.10. Related Trainings

7.7.1. Exporting a Version-Compatible Compilation Database

7.7.2. Importing a Version-Compatible Compilation Database

7.7.3. Creating a Design Partition

7.7.4. Exporting a Design Partition

7.7.5. Reusing a Design Partition

7.7.6. Viewing Quartus Database File Information

7.7.7. Clearing Compilation Results

Visible to Intel only — GUID: lbx1666103856259

Ixiasoft

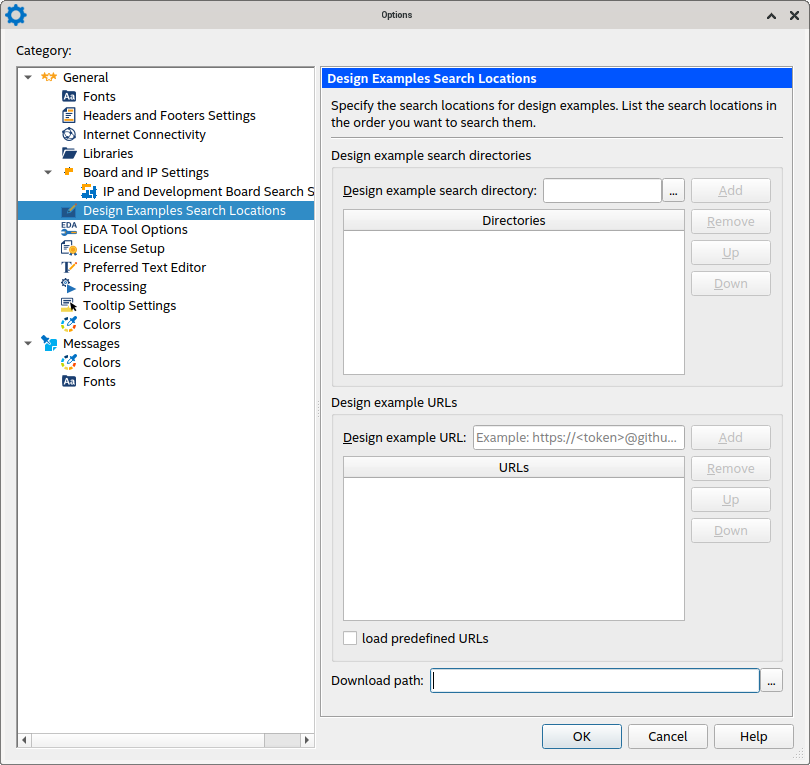

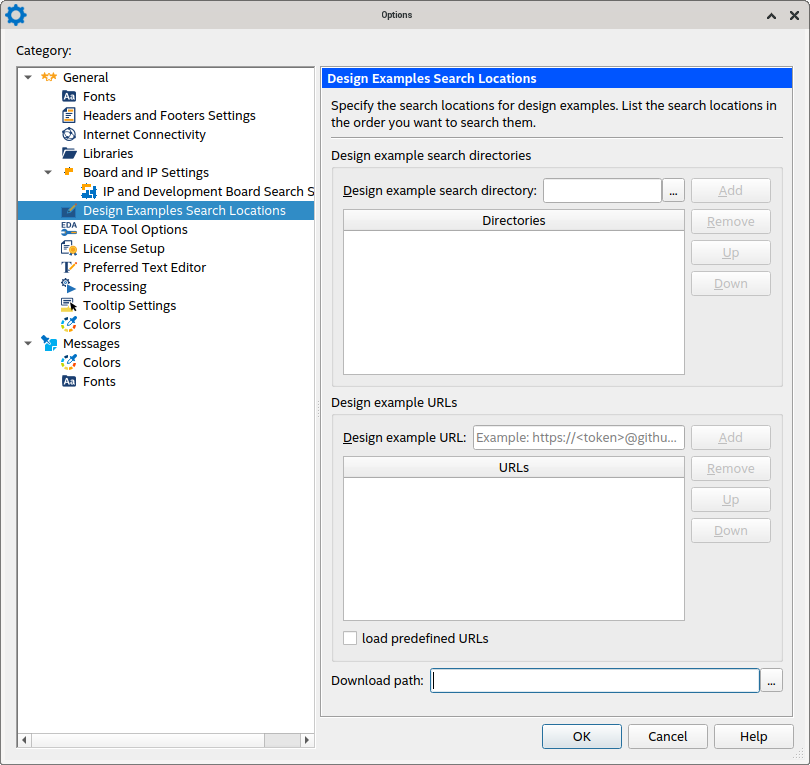

5.1.1.3.2. Design Examples Search Locations

The Quartus® Prime software supports example designs that come from GitHub*, allowing you to register one or more GitHub URLs, including those that require a token for access. The Quartus® Prime software populates the list of designs in the Design Example dialog of the New Project Wizard. Download the design examples from the repositories to a local directory in the .zip format and access them without requiring Internet access. Specify options that determine how the Quartus® Prime software accesses available design examples.

Click File > New Project Wizard > Design Example > Family, Device, and Board Settings > More Settings > Design Example Search Location > .

Figure 35. Design Examples Search Locations Page

| Option | Description |

|---|---|

| Design Example search directory | Specifies the local directories that the Quartus® Prime software searches for design examples. This setting determines which directories you include in search when using the New Project Wizard to start a project from an existing design example. Click Add, Remove, Up, or Down to change the search order and contents in the Directories list. |

| Directories | Lists the various directories that you include in the design example search path for the New Project Wizard. |

| Design example URL | Specifies the GitHub repository URL. If your GitHub repository requires a token, the format for this text field is <TOKEN>@github.com/<repositoy_name>. |

| URLs | Lists various Internet locations where the Quartus® Prime software searches for design examples repositories. |

| Load Predefined URLs | Allows the Quartus® Prime software to read a list of predefined design examples URLs that contain well-known and thoroughly-tested design examples. |

| Download path | Specifies the path for download of online design examples. |