A newer version of this document is available. Customers should click here to go to the newest version.

Visible to Intel only — GUID: mwh1409960620169

Ixiasoft

Visible to Intel only — GUID: mwh1409960620169

Ixiasoft

4.11.1. Generating IP Simulation Files

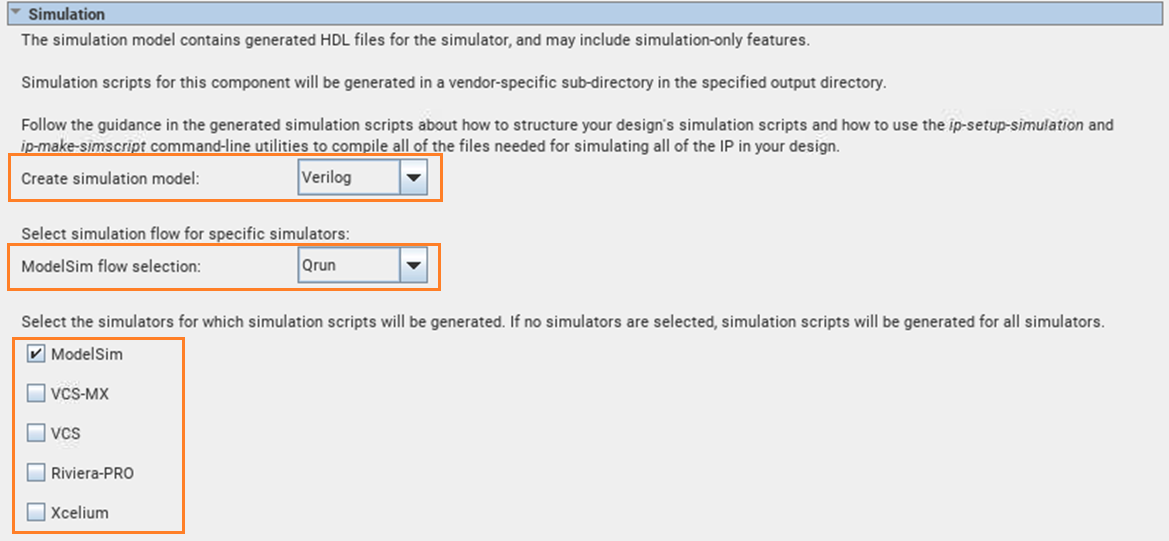

- To specify your supported simulator and options for design simulation file generation, click Assignment > Settings > EDA Tool Settings > Simulation.

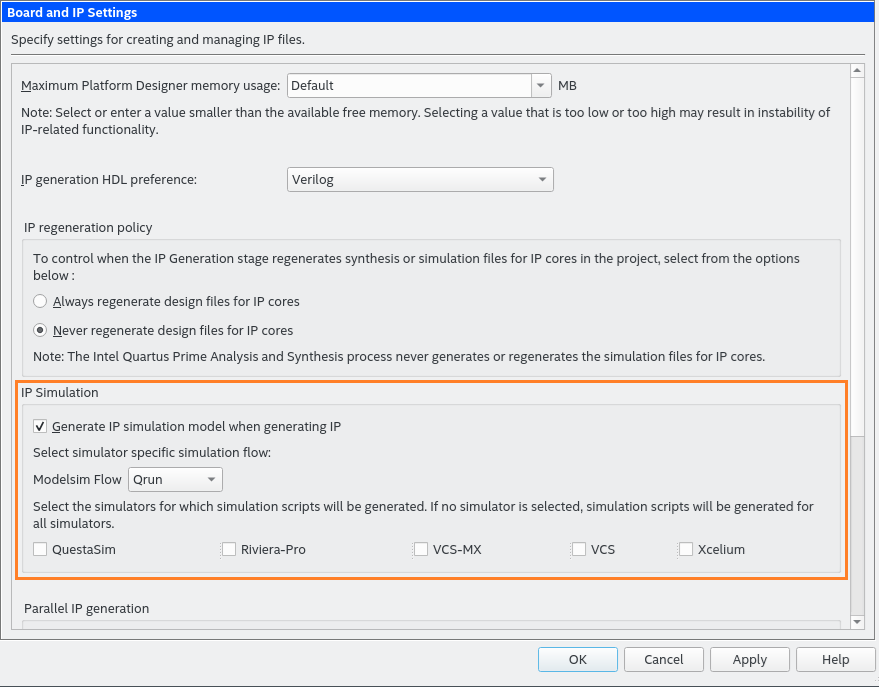

- To specify your supported simulator and options for IP simulation file generation, click Assignments > Settings > Board and IP Settings > IP Simulation and specify the following:

- To enable automatic generation of simulation models for all IP in the project when you generate IP during compilation, turn on the Generate IP simulation model when generating IP option.

- To specify one or more supported simulators for which to generate setup scripts, turn on one or more simulator option, or disable all simulator options to generate scripts for all simulators automatically.

- To generate the simulation files, click Processing > Start Compilation to compile the design. The simulation models and setup scripts for the Intel FPGA IP generate in the <your_project>/<ip name>/sim/<vendor> directory.

You can optionally override these project-level IP Settings when you generate HDL for individual IP cores with the IP Parameter Editor. Prior to generation, you can specify a supported simulator, or specify no simulator to generate the setup scripts for all simulators in the parameter editor.