Visible to Intel only — GUID: nfj1538697119068

Ixiasoft

1. About the P-tile Avalon® Intel® FPGA IPs for PCI Express

2. IP Architecture and Functional Description

3. Parameters

4. Interfaces

5. Advanced Features

6. Troubleshooting/Debugging

7. Document Revision History for the P-tile Avalon® Memory-mapped Intel FPGA IP for PCI Express User Guide

A. Configuration Space Registers

4.1. Overview

4.2. Clocks and Resets

4.3. Avalon® -MM Interface

4.4. Serial Data Interface

4.5. Hard IP Status Interface

4.6. Interrupt Interface

4.7. Hot Plug Interface (RP Only)

4.8. Power Management Interface

4.9. Configuration Output Interface

4.10. Hard IP Reconfiguration Interface

4.11. PHY Reconfiguration Interface

A.2.1. Intel-Defined VSEC Capability Header (Offset 00h)

A.2.2. Intel-Defined Vendor Specific Header (Offset 04h)

A.2.3. Intel Marker (Offset 08h)

A.2.4. JTAG Silicon ID (Offset 0x0C - 0x18)

A.2.5. User Configurable Device and Board ID (Offset 0x1C - 0x1D)

A.2.6. General Purpose Control and Status Register (Offset 0x30)

A.2.7. Uncorrectable Internal Error Status Register (Offset 0x34)

A.2.8. Uncorrectable Internal Error Mask Register (Offset 0x38)

A.2.9. Correctable Internal Error Status Register (Offset 0x3C)

A.2.10. Correctable Internal Error Mask Register (Offset 0x40)

Visible to Intel only — GUID: nfj1538697119068

Ixiasoft

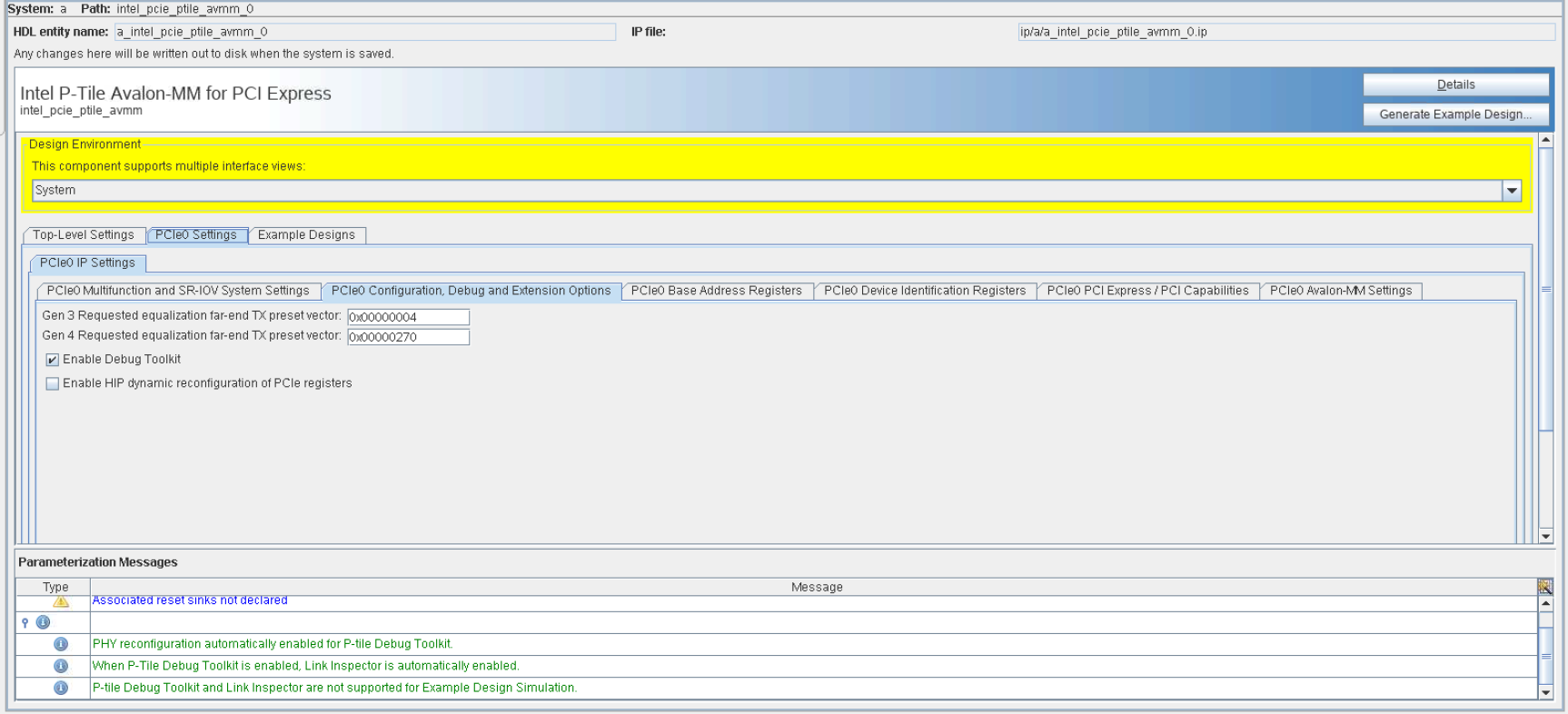

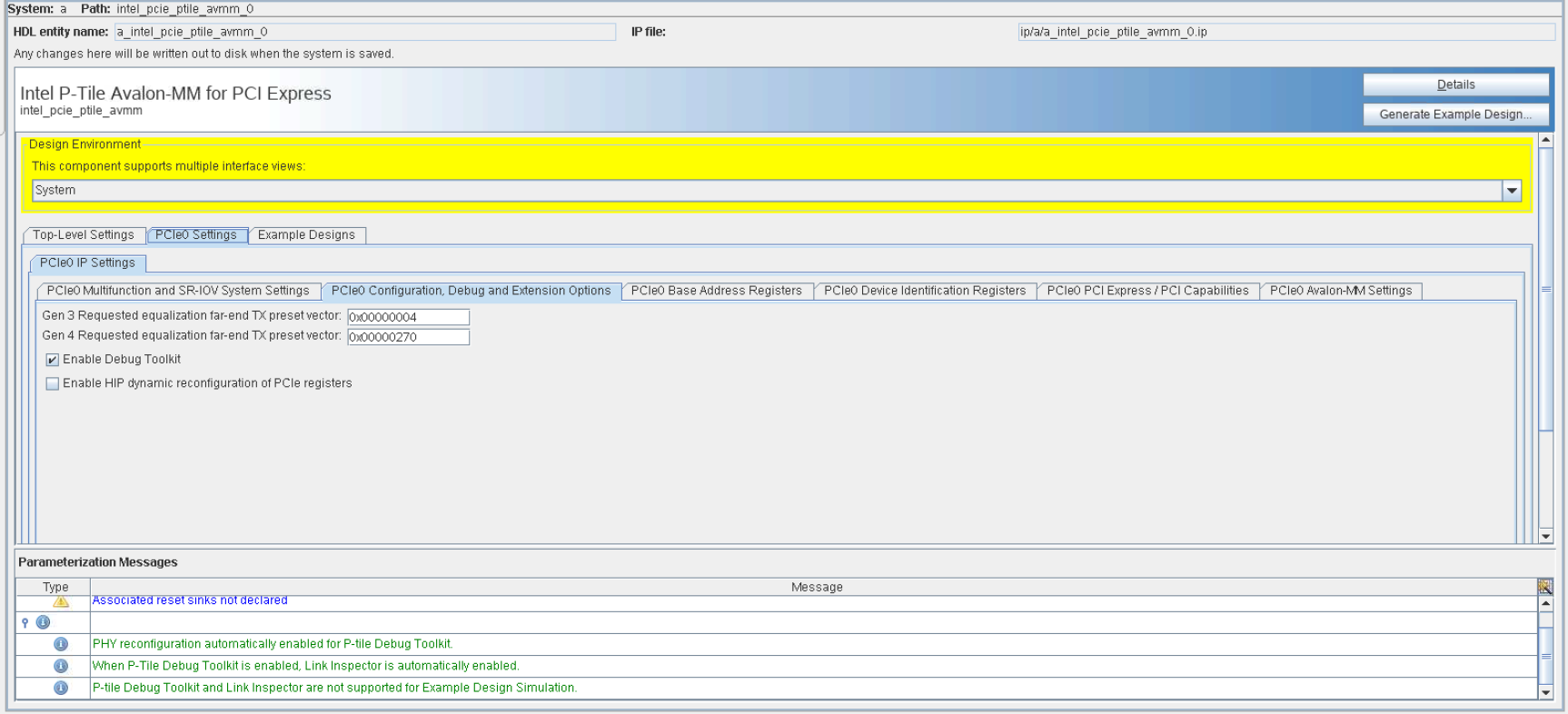

3.2.4. Configuration, Debug and Extension Options

| Parameter | Value | Default Value | Description |

|---|---|---|---|

| Gen 3 Requested equalization far-end TX preset vector | 0 - 65535 | 0x00000004 | Specifies the Gen 3 requested phase 2/3 far-end TX preset vector. Choosing a value different from the default is not recommended for most designs. |

| Gen 4 Requested equalization far-end TX preset vector | 0 - 65535 | 0x00000270 | Specifies the Gen 4 requested phase 2/3 far-end TX preset vector. Choosing a value different from the default is not recommended for most designs. |

| Port 1 REFCLK Init Active | True/False | True | If this parameter is True (default), the refclk1 is stable after pin_perst and is free-running. This parameter must be set to True for Type A/B/C systems. If this parameter is False, refclk1 is only available later in User Mode. This parameter must be set to False for Type D systems and for the 2x8 Hard IP mode where only Port 0 is used and refclk1 is unconnected or not driven. This parameter is only available in the PCIe1 Settings tab for a X8X8 topology.

Note: Refer to Appendix E for more details regarding the bifurcation feature and its usage.

|

| Strip ECRC | True/False | False | Strip off the ECRC field from the TLP payload when the TD bit is set. Note that this option is only available in the TLP-Bypass mode. |

Figure 16. Configuration, Debug and Extension Parameters (with Debug Toolkit Enabled)