AN 709: HPS SoC Boot Guide - Cyclone V SoC Development Kit

ID

683265

Date

1/27/2016

Public

Visible to Intel only — GUID: lro1418631690400

Ixiasoft

1.5.5.1. Overview

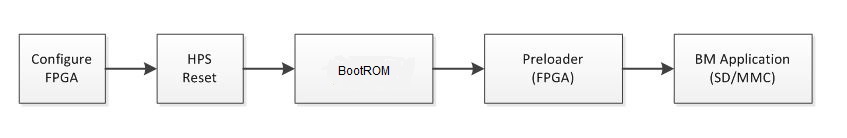

In this example, we have the Preloader running from FPGA, but then it loads the bare-metal image that we have on SD/MMC custom partition. If desired, the Preloader can also be configured to jump to an absolute address, that may also be located in the FPGA fabric address space.

The boot flow of this example is described below:

Figure 12. Boot Flow

In order to achieve booting from FPGA the following are required:

- BSEL needs to be set to 0x1 - Boot from FPGA

- FPGA image needs to have an on-chip memory instantiated, mapped at offset 0x0 behind the HPS2FPGA bridge. The memory needs to be loaded with Preloader executable binary

- FPGA image needs to drive the value of the following two signals to HPS, since they are required by Boot ROM:

- f2h_boot_from_fpga_ready - indicates that the Boot ROM can boot from FPGA if BSEL = 0x1

- f2h_boot_from_fpga_on_failure - indicates that the Boot ROM can boot from FPGA as a fallback, if it failed booting from the selected BSEL

- Preloader executable (.text) section needs to be linked to address 0xC0000000 (equivalent of offset 0x0 behind the HPS2FPGA bridge)

- Preloader executable (.data) sections need to be linked to address 0xFFFF0000 (the HPS OCRAM)

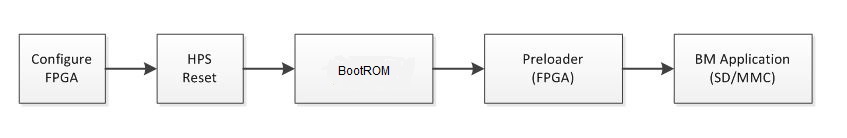

The complete flow is described in the following figure:

Figure 13. Complete Flow

Note: The design needs to be compiled once in order to obtain the handoff folder, which is used to generate the Preloader. Once the Preloader hex file is obtained, the design is compiled again in order to have the FPGA memory initialized with the contents of the hex file.