Visible to Intel only — GUID: coj1707242724835

Ixiasoft

1.2.1. Timing Path and Clock Analysis

1.2.2. Clock Setup Analysis

1.2.3. Clock Hold Analysis

1.2.4. Recovery and Removal Analysis

1.2.5. Multicycle Path Analysis

1.2.6. Metastability Analysis

1.2.7. Timing Pessimism

1.2.8. Clock-As-Data Analysis

1.2.9. Multicorner Timing Analysis

1.2.10. Time Borrowing

2.1. Using Timing Constraints throughout the Design Flow

2.2. Timing Analysis Flow

2.3. Applying Timing Constraints

2.4. Timing Constraint Descriptions

2.5. Timing Report Descriptions

2.6. Scripting Timing Analysis

2.7. Using the Quartus® Prime Timing Analyzer Document Revision History

2.8. Quartus® Prime Pro Edition User Guide: Timing Analyzer Archive

2.4.4.5.1. Default Multicycle Analysis

2.4.4.5.2. End Multicycle Setup = 2 and End Multicycle Hold = 0

2.4.4.5.3. End Multicycle Setup = 2 and End Multicycle Hold = 1

2.4.4.5.4. Same Frequency Clocks with Destination Clock Offset

2.4.4.5.5. Destination Clock Frequency is a Multiple of the Source Clock Frequency

2.4.4.5.6. Destination Clock Frequency is a Multiple of the Source Clock Frequency with an Offset

2.4.4.5.7. Source Clock Frequency is a Multiple of the Destination Clock Frequency

2.4.4.5.8. Source Clock Frequency is a Multiple of the Destination Clock Frequency with an Offset

2.5.1. Report Fmax Summary

2.5.2. Report Timing

2.5.3. Report Timing By Source Files

2.5.4. Report Data Delay

2.5.5. Report Net Delay

2.5.6. Report Clocks and Clock Network

2.5.7. Report Clock Transfers

2.5.8. Report Metastability

2.5.9. Report CDC Viewer

2.5.10. Report Asynchronous CDC

2.5.11. Report Logic Depth

2.5.12. Report Neighbor Paths

2.5.13. Report Register Spread

2.5.14. Report Route Net of Interest

2.5.15. Report Retiming Restrictions

2.5.16. Report Register Statistics

2.5.17. Report Pipelining Information

2.5.18. Report Time Borrowing Data

2.5.19. Report Exceptions and Exceptions Reachability

2.5.20. Report Bottlenecks

2.5.21. Check Timing

2.5.22. Report SDC

Visible to Intel only — GUID: coj1707242724835

Ixiasoft

2.3.5.2.5. Importing a Design Partition with Entity-bound Constraints

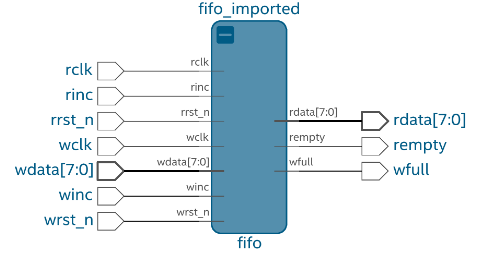

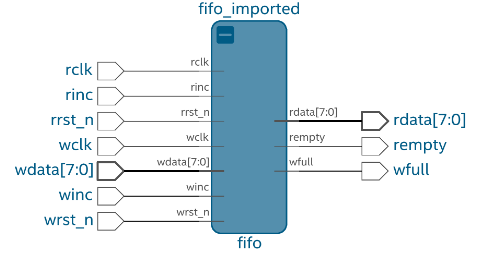

Importing a partition with entity-bound SDC files requires that you define a black box wrapper for the entity in your design. This wrapper declares a partition in which the data from the imported partition is utilized. Consider the following example with an entity named fifo_imported:

Figure 83. Example of an Entity Named fifo_imported

To import a design partition with entity-bound constraints, perform these steps:

- To run design synthesis, click Analysis & Synthesis on the Compilation Dashboard.

- To create a new partition within the wrapper entity, click Assignments > Design Partitions Window and specify the following options on the Assignments View tab:

- Specify the Partition Name and the Hierarchy Path of the entity instance.

- Specify Default for the partition Type.

- Specify synthesized in the Preservation Level column.

- Specify the .qdb file from the previous project as the Partition Database File

Figure 84. Assignments View of the Design Partition Dialog

- To run a full compilation, click Compile Design on the Compilation Dashboard. The Timing Analyzer appears automatically following successful compilation.

- Verify the correct application of the entity-bound SDC file assignment in the SDC File List report.

Figure 85. SDC File List Report in the Timing Analyzer