Intel® Quartus® Prime Pro Edition User Guide: Design Compilation

ID

683236

Date

9/26/2022

Public

A newer version of this document is available. Customers should click here to go to the newest version.

Visible to Intel only — GUID: ytj1533931508178

Ixiasoft

2.1. Compilation Overview

2.2. Using the Compilation Dashboard

2.3. Design Netlist Infrastructure (Beta)

2.4. Design Synthesis

2.5. Design Place and Route

2.6. Incremental Optimization Flow

2.7. Fast Forward Compilation Flow

2.8. Full Compilation Flow

2.9. Exporting Compilation Results

2.10. Integrating Other EDA Tools

2.11. Synthesis Language Support

2.12. Compiler Optimization Techniques

2.13. Synthesis Settings Reference

2.14. Fitter Settings Reference

2.15. Design Compilation Revision History

2.9.1. Exporting a Version-Compatible Compilation Database

2.9.2. Importing a Version-Compatible Compilation Database

2.9.3. Creating a Design Partition

2.9.4. Exporting a Design Partition

2.9.5. Reusing a Design Partition

2.9.6. Viewing Quartus Database File Information

2.9.7. Clearing Compilation Results

3.1. Factors Affecting Compilation Results

3.2. Strategies to Reduce the Overall Compilation Time

3.3. Reducing Synthesis Time and Synthesis Netlist Optimization Time

3.4. Reducing Placement Time

3.5. Reducing Routing Time

3.6. Reducing Static Timing Analysis Time

3.7. Setting Process Priority

3.8. Reducing Compilation Time Revision History

Visible to Intel only — GUID: ytj1533931508178

Ixiasoft

2.9.3. Creating a Design Partition

A design partition is a logical, named, hierarchical boundary that you can assign to an instance in your design. Defining a design partition allows you to optimize and lock down the compilation results for individual blocks. You can then optionally export the compilation results of a design partition for reuse in another context, such as reuse in another project.

Figure 88. Design Partitions in Design Hierarchy

Follow these steps to create and modify design partitions:

- In the Intel® Quartus® Prime software, open the project that you want to partition.

- Generate synthesis or final compilation results by running one of the following commands:

- Click Processing > Start > Start Analysis & Synthesis to generate synthesized compilation results.

- Click Processing > Start Compilation to generate final compilation results.

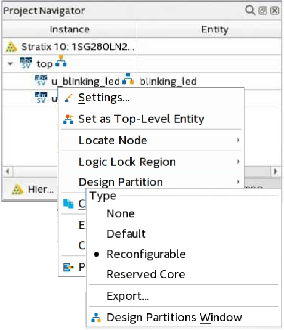

- In the Project Navigator, right-click an instance in the Hierarchy tab, click Design Partition > Set as Design Partition.

Figure 89. Creating a Design Partition from the Project Hierarchy

- To view and edit all design partitions in the project, click Assignments > Design Partitions Window.

Figure 90. Design Partitions Window

- Specify the properties of the design partition in the Design Partitions Window. The following settings are available:

Table 27. Design Partition Settings Option Description Partition Name Specifies the partition name. Each partition name must be unique and consist of only alphanumeric characters. The Intel® Quartus® Prime software automatically creates a top-level (|) "root_partition" for each project revision. Hierarchy Path Specifies the hierarchy path of the entity instance that you assign to the partition. You specify this value in the Create New Partition dialog box. The root partition hierarchy path is |. Type Double-click to specify one of the following partition types that control how the Compiler processes and implements the partition: - Default—Identifies a standard partition. The Compiler processes the partition using the associated design source files.

- Reconfigurable—Identifies a reconfigurable partition in a partial reconfiguration flow. Specify the Reconfigurable type to preserve synthesis results, while allowing refit of the partition in the PR flow.

- Reserved Core—Identifies a partition in a block-based design flow that is reserved for core development by a Consumer reusing the device periphery.

Preservation Level Specifies one of the following preservation levels for the partition: - Not Set—specifies no preservation level. The partition compiles from source files.

- synthesized—the partition compiles using the synthesized snapshot.

- final—the partition compiles using the final snapshot.

With Preservation Level of synthesized or final, changes to the source code do not appear in the synthesis.

Empty Specifies an empty partition that the Compiler skips. This setting is incompatible with the Reserved Core and Partition Database File settings for the same partition. The Preservation Level must be Not Set. An empty partition cannot have any child partitions. Partition Database File Specifies a Partition Database File (.qdb) that the Compiler uses during compilation of the partition. You export the .qdb for the stage of compilation that you want to reuse (synthesized or final). Assign the .qdb to a partition to reuse those results in another context. Entity Re-binding - PR Flow—specifies the entity that replaces the default persona in each implementation revision.

- Root Partition Reuse Flow —specifies the entity that replaces the reserved core logic in the consumer project.

Color Specifies the color-coding of the partition in the Chip Planner and Design Partition Planner displays. Post Synthesis Export File Automatically exports post-synthesis compilation results for the partition to the specified .qdb file each time Analysis & Synthesis runs. You can automatically export any design partition that does not have a preserved parent partition, including the root_partition. Post Final Export File Automatically exports post-final compilation results for the partition to the specified .qdb file each time the final stage of the Fitter runs. You can automatically export any design partition that does not have a preserved parent partition, including the root_partition.