Visible to Intel only — GUID: dmi1461675640527

Ixiasoft

Visible to Intel only — GUID: dmi1461675640527

Ixiasoft

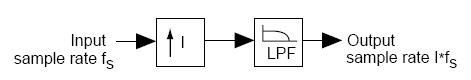

4.1. FIR II IP Core Interpolation Filters

The FIR II IP core implements interpolation filters using a single engine that the different phases timeshare to optimize area. This implementation changes the overall throughput of the filter and the input sample rate. The throughput of the filter is the rate at which the filter generates the output (one output every K clock cycles). The input sample rate is the rate at which the filter processes input data samples (the input needs to be held for L clock cycles).

The values of K and L for the throughput and input sample rate of FIR II interpolation filters depend on the filter architecture.

| Architecture | Equations |

|---|---|

| Fully serial | K = N L = N I |

| Multibit serial | K = N/M L = N I / M |

| Fully parallel | K = 1 L = I |

| Multicycle | K = C L = C I |

For systems that require higher throughput and input data rate, Intel recommends that you use parallel or multicycle variable structures.