Visible to Intel only — GUID: xyl1526349752156

Ixiasoft

2.3.2.1. Using Simulation Signal Activity Data in Power Analysis

2.3.2.2. Signal Activities from RTL (Functional) Simulation, Supplemented by Vectorless Estimation

2.3.2.3. Signal Activities from Vectorless Estimation and User-Supplied Input Pin Activities

2.3.2.4. Signal Activities from User Defaults Only

2.5.1. Complete Design Simulation Power Analysis Flow

2.5.2. Modular Design Simulation Power Analysis Flow

2.5.3. Multiple Simulation Power Analysis Flow

2.5.4. Overlapping Simulation Power Analysis Flow

2.5.5. Partial Design Simulation Power Analysis Flow

2.5.6. Vectorless Estimation Power Analysis Flow

3.4.1. Clock Power Management

3.4.2. Pipelining and Retiming

3.4.3. Architectural Optimization

3.4.4. I/O Power Guidelines

3.4.5. Dynamically Controlled On-Chip Terminations (OCT)

3.4.6. Memory Optimization (M20K/MLAB)

3.4.7. DDR Memory Controller Settings

3.4.8. DSP Implementation

3.4.9. Reducing High-Speed Tile (HST) Usage

3.4.10. Unused Transceiver Channels

3.4.11. Periphery Power reduction XCVR Settings

Visible to Intel only — GUID: xyl1526349752156

Ixiasoft

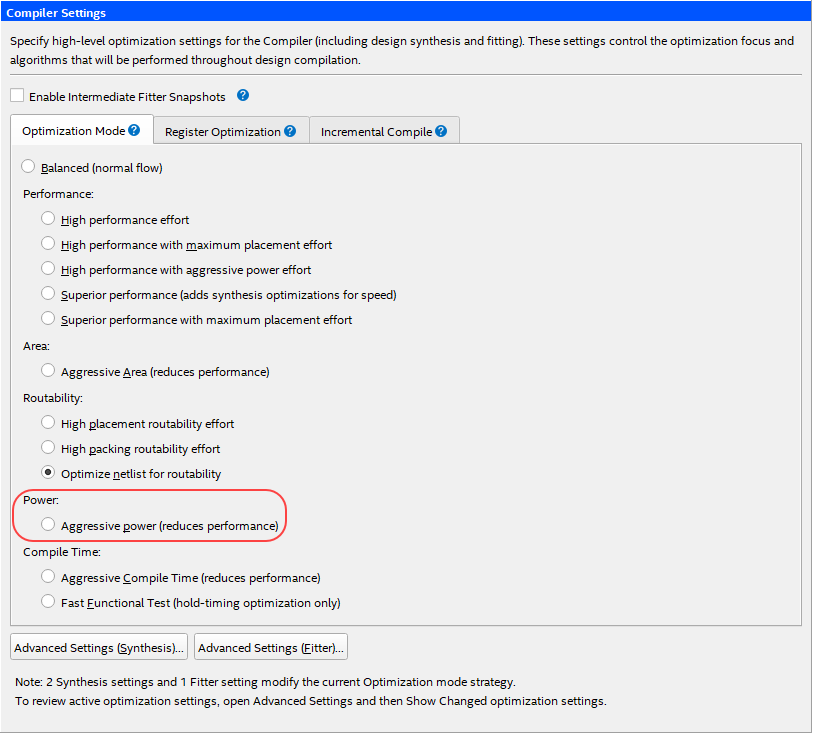

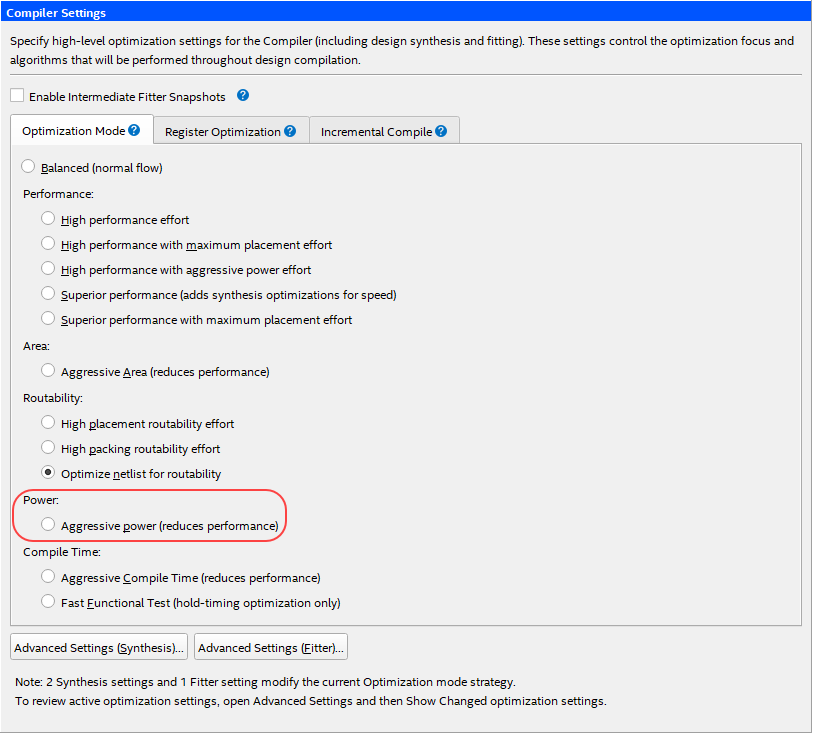

3.3.5. Intel® Quartus® Prime Compiler Settings

The Intel® Quartus® Prime software provides settings that optimize power for the full design.

To set the optimization mode on the Intel® Quartus® Prime software, click Assignments > Settings > Compiler Settings.

Figure 22. Compiler Settings

Aggressive Power (reduces performance)

Makes aggressive effort to optimize synthesis for low power. The Compiler further reduces the routing usage of signals with the highest specified or estimated toggle rates, saving additional dynamic power but potentially affecting performance.