Visible to Intel only — GUID: tcn1522786162335

Ixiasoft

2.3.2.1. Using Simulation Signal Activity Data in Power Analysis

2.3.2.2. Signal Activities from RTL (Functional) Simulation, Supplemented by Vectorless Estimation

2.3.2.3. Signal Activities from Vectorless Estimation and User-Supplied Input Pin Activities

2.3.2.4. Signal Activities from User Defaults Only

2.5.1. Complete Design Simulation Power Analysis Flow

2.5.2. Modular Design Simulation Power Analysis Flow

2.5.3. Multiple Simulation Power Analysis Flow

2.5.4. Overlapping Simulation Power Analysis Flow

2.5.5. Partial Design Simulation Power Analysis Flow

2.5.6. Vectorless Estimation Power Analysis Flow

3.4.1. Clock Power Management

3.4.2. Pipelining and Retiming

3.4.3. Architectural Optimization

3.4.4. I/O Power Guidelines

3.4.5. Dynamically Controlled On-Chip Terminations (OCT)

3.4.6. Memory Optimization (M20K/MLAB)

3.4.7. DDR Memory Controller Settings

3.4.8. DSP Implementation

3.4.9. Reducing High-Speed Tile (HST) Usage

3.4.10. Unused Transceiver Channels

3.4.11. Periphery Power reduction XCVR Settings

Visible to Intel only — GUID: tcn1522786162335

Ixiasoft

3.3.6. Assignment Editor Options

The Assignment Editor allows you to select Optimization Technique & Synthesis Power Optimization for individual modules. With this feature, you can focus on the parts of the design that require more work.

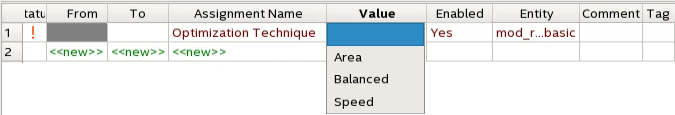

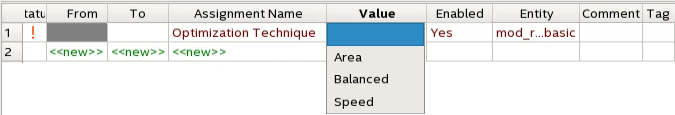

The Optimization Technique logic option specifies the overall optimization goal for Analysis & Synthesis: attempt to maximize performance or minimize logic usage.

Figure 23. Optimization Technique Options

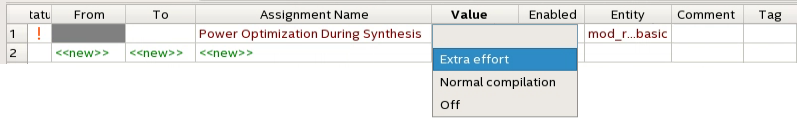

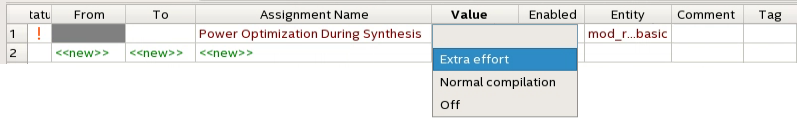

The Power Optimization During Synthesis logic option determines how aggressively Analysis & Synthesis optimizes the design for power.

Figure 24. Power Optimization During Synthesis Options

| Settings | Description | Optimization Techniques Included |

|---|---|---|

| Off | The Compiler does not perform netlist, placement, or routing optimizations to minimize power. | - |

| Normal compilation (Default) | The Compiler applies low compute effort algorithms to minimize power through netlist optimizations that do not reduce design performance. |

|

| Extra effort | Besides the techniques in the Normal compilation setting, the Compiler applies high-compute-effort algorithms to minimize power through netlist optimizations. Selecting this option might impact performance. |

|