Visible to Intel only — GUID: mwh1410470995278

Ixiasoft

2.1.2.1. Specify Instance-Specific Constraints in Assignment Editor

2.1.2.2. Specify NoC Constraints in NoC Assignment Editor

2.1.2.3. Specify I/O Constraints in Pin Planner

2.1.2.4. Plan Interface Constraints in Interface Planner and Tile Interface Planner

2.1.2.5. Adjust Constraints with the Chip Planner

2.1.2.6. Constraining Designs with the Design Partition Planner

4.2.1. Assigning to Exclusive Pin Groups

4.2.2. Assigning Slew Rate and Drive Strength

4.2.3. Assigning I/O Banks

4.2.4. Changing Pin Planner Highlight Colors

4.2.5. Showing I/O Lanes

4.2.6. Assigning Differential Pins

4.2.7. Entering Pin Assignments with Tcl Commands

4.2.8. Entering Pin Assignments in HDL Code

Visible to Intel only — GUID: mwh1410470995278

Ixiasoft

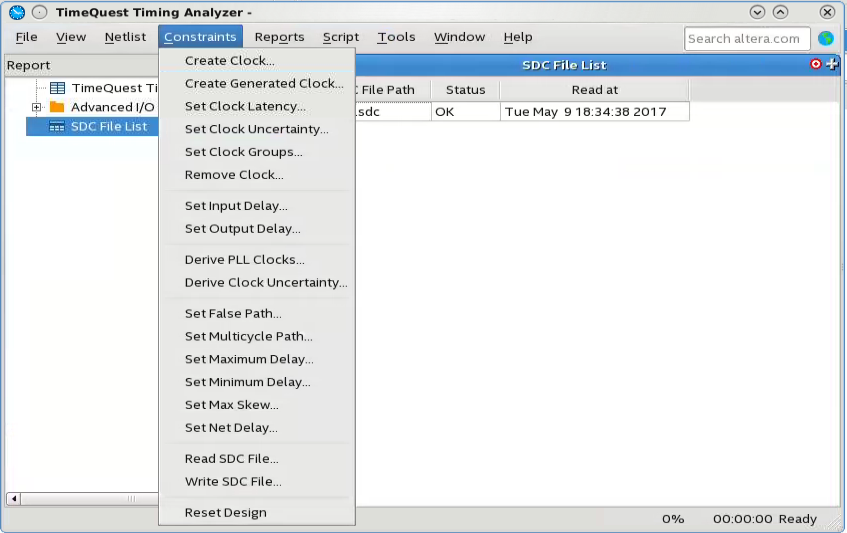

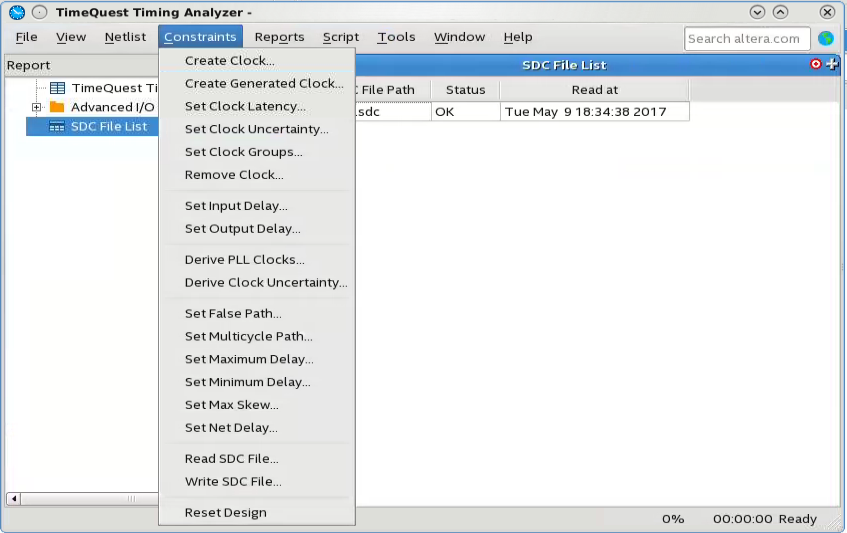

2.1.4. Specifying Timing Constraints in the GUI

You can specify timing constraints in the Timing Analyzer GUI. Click the Constraints menu in the Timing Analyzer to specify timing constraints that you can apply to your project.

Figure 6. Constraint menu in Timing Analyzer

When you specify a constraint in the GUI, the dialog box displays the equivalent SDC command syntax.

Create Clock Dialog Box

Individual timing assignments override project-wide requirements.

- To avoid reporting incorrect or irrelevant timing violations, you can assign timing exceptions to nodes and paths.

- The Timing Analyzer supports point-to-point timing constraints, wildcards to identify specific nodes when making constraints, and assignment groups to make individual constraints to groups of nodes.