Visible to Intel only — GUID: gqr1541811904026

Ixiasoft

Visible to Intel only — GUID: gqr1541811904026

Ixiasoft

4.7.1. Completion Timeout Interface

The P-Tile IP for PCIe features a Completion timeout mechanism to keep track of Non-Posted requests sent by the user application and the corresponding Completions received. When the P-Tile IP detects a Completion timeout, it notifies the user application by asserting the cpl_timeout_o signal.

When a Completion timeout happens, the user application can use the Avalon® -MM Completion Timeout Interface (for each port) to access the Completion timeout FIFO in the Hard IP to get more detailed information about the event and update the AER capability registers if required. After the completion timeout FIFO becomes empty, the IP core deasserts the cpl_timeout_o signal.

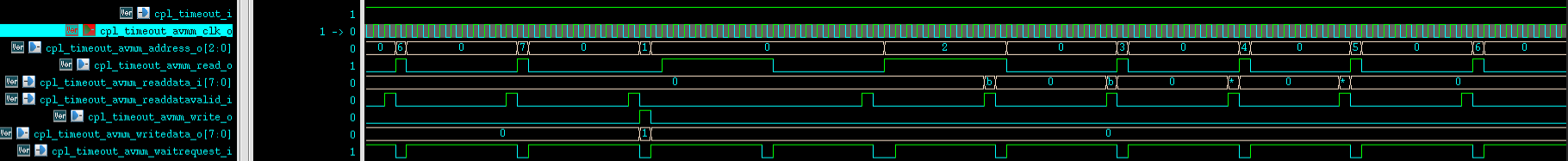

The cpl_timeout_avmm interface is synchronized to the cpl_timeout_avmm_clk_i clock.

Example:

When cpl_timeout_o is asserted, the user application can issue an Avalon® -MM Read to retrieve information from the Completion FIFO. Then, it can issue an Avalon® -MM Write to write 1 to bit[0] of the CONTROL register to get access to the next data.

The application logic must read the completion timeout interface status register to track the FIFO full and empty markers. Once the completion timeout FIFO indicates that it is full, any subsequent completion timeout packet information will not be captured by the timeout interface.

| Signal Name | Direction | Description | Clock domain | EP/RP/BP |

|---|---|---|---|---|

| cpl_timeout_o | O | Indicates the event that the completion TLP for a request has not been received within the expected time window. The IP core asserts this signal as long as the completion timeout FIFO in the Hard IP is not empty. You can obtain more details about the completion timeout event by looking at the signals on the completion timeout Avalon® -MM interface (listed below). |

coreclkout_hip | EP/RP |

| cpl_timeout_avmm_read_i | I | Avalon® -MM read enable. | cpl_timeout_avmm_clk_i | EP/RP |

| cpl_timeout_avmm_readdata_o[7:0] | O | Avalon® -MM read data outputs. | cpl_timeout_avmm_clk_i | EP/RP |

| cpl_timeout_avmm_readdata_valid_o | O | This signal qualifies the cpl_timeout_avmm_readdata_o signals into the Application Layer. | cpl_timeout_avmm_clk_i | EP/RP |

| cpl_timeout_avmm_write_i | I | Avalon® -MM write enable. | cpl_timeout_avmm_clk_i | EP/RP |

| cpl_timeout_avmm_writedata_i[7:0] | I | Avalon® -MM write data inputs. | cpl_timeout_avmm_clk_i | EP/RP |

| cpl_timeout_avmm_addr_i[20:0] | I | Avalon® -MM address inputs. [20:3] : Reserved. Tie them to 0. [2:0] : Address for the FIFO register. Refer to the address map table below for more details. |

cpl_timeout_avmm_clk_i | EP/RP |

| cpl_timeout_avmm_waitrequest_o | O | When asserted, this signal indicates the IP core is not ready to take any request. | cpl_timeout_avmm_clk_i | EP/RP |

| cpl_timeout_avmm_clk_i | I | Avalon® -MM clock. 50 MHz - 125 MHz (Range) 100 MHz (Recommended) This clock must be provided with or connected to a clock source when you enable this interface. |

EP/RP |

| Address | Name | Access Type | Description |

|---|---|---|---|

| 0x0 | STATUS | RO | [7:2] : Reserved [1] : Completion timeout FIFO full [0] : Completion timeout FIFO empty |

| 0x1 | CONTROL | WO | [7:1] : Reserved [0] : Read (popping data from the FIFO). You need to read all the information regarding the timed out request before writing 1 to bit 0 of the CONTROL register. Writing to bit 0 of the CONTROL register makes the next data appear. |

| 0x2 | VF | RO | [7:0] : vfunc_num[7:0] Virtual Function number for the VF that initiates the non-posted transaction for which the completion timeout is observed. |

| 0x3 | PF | RO | [7] : vfunc_active [6] : Reserved [5:3] : func_num[2:0] Physical function number (least significant 8 bits) for the PF that initiates the non-posted transaction for which the completion timeout is observed. [2:0] : vfunc_num[10:8] Virtual Function number (most significant 3 bits) for the VF that initiates the memory read request for which the completion timeout is observed. |

| 0x4 | LEN1 | RO | [7:0] : cpl_lenn[7:0] Transfer length in bytes (least significant 8 bits), of the expected completion that timed out for the non-posted transaction. For a split completion, it indicates the number of bytes remaining to be delivered when the completion timed out (Max length is Max Read request size. Ex: 4K Bytes = 2^12 bytes) |

| 0x5 | LEN2 | RO | [7:4] : Reserved [3:0] : cpl_lenn[11:8] Transfer length in bytes (most significant 4 bits), of the expected completion that timed out for the non-posted transaction. For a split completion, it indicates the number of bytes remaining to be delivered when the completion timed out (Max length is Max Read request size. Ex: 4K Bytes = 2^12 bytes) |

| 0x6 | TAG1 | RO | [7:0] : cpl_tag[7:0] Tag ID (least significant 8 bits) of the expected completion that timed out for the non-posted transaction. |

| 0x7 | TAG2 | RO | [7:5] : cpl_tc[2:0] Traffic class of the expected completion that timed out for the non-posted transaction. [4:3] : cpl_attr[1:0] Attribute of the expected completion that timed out for the non-posted transaction. ID based ordering is not supported. [4] -> Relaxed ordering, [3] -> No Snoop [2] : Reserved [1:0]: cpl_tag[9:8] Tag ID (most significant 2 bits) of the expected completion that timed out for the non-posted transaction. |