Visible to Intel only — GUID: kwj1478098325374

Ixiasoft

1.1. Introduction to Custom Platforms

1.2. OpenCL System Architecture

1.3. Hierarchical Structure of the Intel® Arria® 10 GX FPGA Development Kit Reference Platform's Hardware

1.4. Intel® Quartus® Prime Software Revisions Describing the Custom Platform

1.5. Intel® FPGA SDK for OpenCL™ and User Environment Setup

1.6. Intel® Arria® 10 Custom Platform Project Setup and Customization Procedure

1.7. Intel® Arria® 10 Custom Platform Customization Example

1.8. Updating Your Custom Platform to Target a Different Device

1.9. Migrating the Custom Platform between Different Intel® Quartus® Prime Software Versions

1.10. Document Revision History for Compiling and Customizing an Intel® Arria® 10 Custom Platform for OpenCL*

1.7.1. Modifying the board.qsys File in the Custom Platform

1.7.2. Modifying the Kernel (freeze_wrapper.v and board_spec.xml)

1.7.3. Updating the Top-Level I/O Ring with the Modified board.qsys and freeze_wrapper.v Files

1.7.4. Updating the Original Custom Platform Directory with the New Custom Platform Modifications

1.7.5. Compilation Log Files

1.7.6. Analyzing the Results from Compilation

1.7.1.1. Opening an Existing Intel® Quartus® Prime Project and the board.qsys Platform Designer System Design

1.7.1.2. Adding the Avalon® -ST Single Clock FIFO Component into the Platform Designer System

1.7.1.3. Connecting the Avalon® -ST Single Clock FIFO Component's Exported Signals in the Top-Level Platform Designer System

1.7.2.1. Opening an Existing Intel® Quartus® Prime Project and the kernel_system.qsys Platform Designer System Design

1.7.2.2. Adding an Avalon® -ST Adapter Component into the Platform Designer System

1.7.2.3. Connecting the Avalon® -ST Adapter Component's Exported Signals in the Top-Level Platform Designer System

1.7.2.4. Modifying the board_spec.xml File

1.7.2.5. Modifying the freeze_wrapper.v File

Visible to Intel only — GUID: kwj1478098325374

Ixiasoft

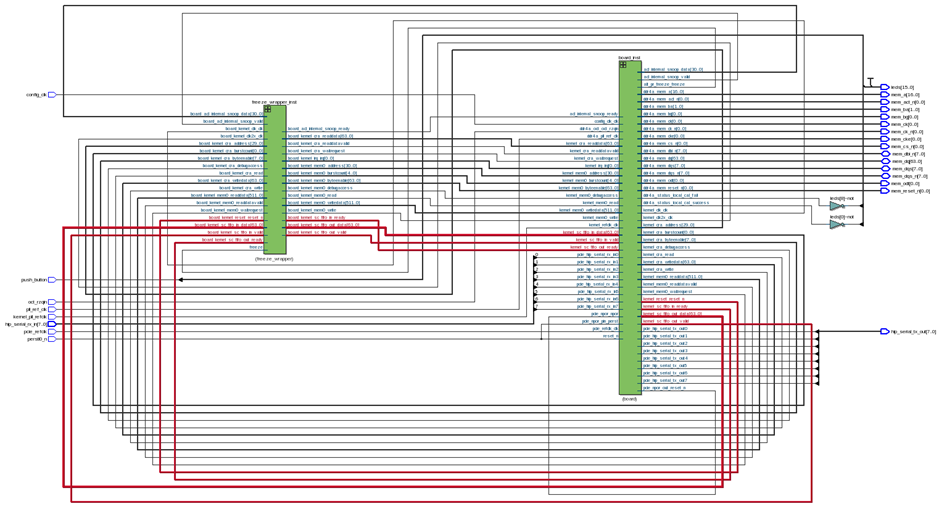

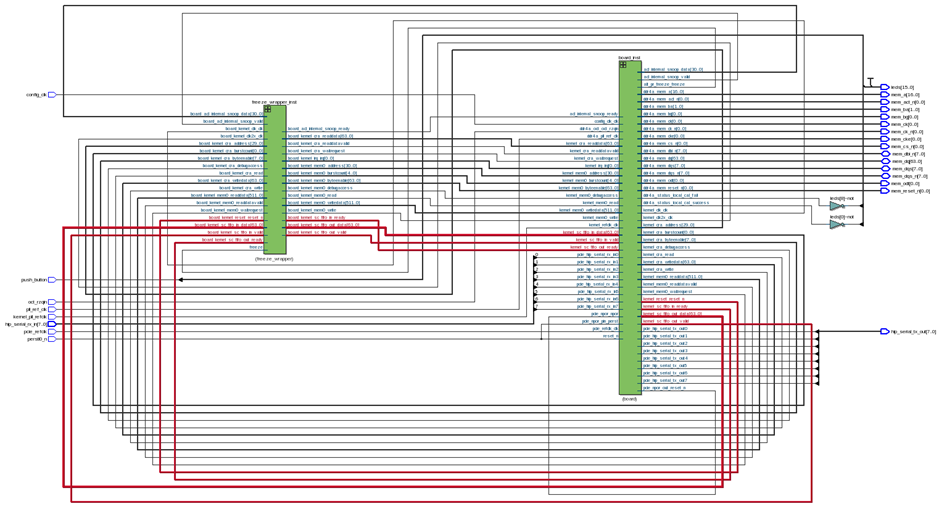

1.7.3. Updating the Top-Level I/O Ring with the Modified board.qsys and freeze_wrapper.v Files

Add ports and signals to the board and freeze_wrapper instances in the top.v file.

- Open the top.v file in the Intel® Quartus® Prime Pro Edition software.

- Add the new ports to the board instance.

- Add the new ports to the freeze_wrapper instance.

- Add signal (wires) to connect the board instance to the freeze_wrapper instance.

- Save the top.v file.

- In the Intel® Quartus® Prime Pro Edition software, run Analysis and Synthesis to check the syntax of your RTL and fix any errors.

Figure 11. RTL Netlist of the New Board Interface Connected to the New Freeze Wrapper