Visible to Intel only — GUID: kly1462519667619

Ixiasoft

1. Intel® Agilex™ 7 Variable Precision DSP Blocks Overview

2. Intel® Agilex™ 7 Variable Precision DSP Blocks Architecture

3. Intel® Agilex™ 7 Variable Precision DSP Blocks Operational Modes

4. Intel® Agilex™ 7 Variable Precision DSP Blocks Design Considerations

5. Native Fixed Point DSP Intel® Agilex™ FPGA IP Core References

6. Multiply Adder Intel® FPGA IP Core References

7. ALTMULT_COMPLEX Intel® FPGA IP Core Reference

8. LPM_MULT Intel® FPGA IP Core References

9. LPM_DIVIDE (Divider) Intel FPGA IP Core

10. Native Floating Point DSP Intel® Agilex™ FPGA IP References

11. Intel® Agilex™ 7 Variable Precision DSP Blocks User Guide Archives

12. Document Revision History for the Intel Agilex® 7 Variable Precision DSP Blocks User Guide

2.1.1. Input Register Bank for Fixed-point Arithmetic

2.1.2. Pipeline Registers for Fixed-point Arithmetic

2.1.3. Pre-adder for Fixed-point Arithmetic

2.1.4. Internal Coefficient for Fixed-point Arithmetic

2.1.5. Multipliers for Fixed-point Arithmetic

2.1.6. Adder or Subtractor for Fixed-point Arithmetic

2.1.7. Accumulator, Chainout Adder, and Preload Constant for Fixed-point Arithmetic

2.1.8. Systolic Register for Fixed-point Arithmetic

2.1.9. Double Accumulation Register for Fixed-point Arithmetic

2.1.10. Output Register Bank for Fixed-point Arithmetic

2.2.1. Input Register Bank for Floating-point Arithmetic

2.2.2. Pipeline Registers for Floating-point Arithmetic

2.2.3. Multipliers for Floating-point Arithmetic

2.2.4. Adder or Subtractor for Floating-point Arithmetic

2.2.5. Output Register Bank for Floating-point Arithmetic

2.2.6. Exception Handling for Floating-point Arithmetic

3.2.2.1. FP16 Supported Precision Formats

3.2.2.2. Sum of Two FP16 Multiplication Mode

3.2.2.3. Sum of Two FP16 Multiplication with FP32 Addition Mode

3.2.2.4. Sum of Two FP16 Multiplication with Accumulation Mode

3.2.2.5. FP16 Vector One Mode

3.2.2.6. FP16 Vector Two Mode

3.2.2.7. FP16 Vector Three Mode

5.1. Native Fixed Point DSP Intel® Agilex™ FPGA IP Release Information

5.2. Supported Operational Modes

5.3. Maximum Input Data Width for Fixed-point Arithmetic

5.4. Maximum Output Data Width for Fixed-point Arithmetic

5.5. Parameterizing Native Fixed Point DSP IP

5.6. Native Fixed Point DSP Intel® Agilex™ FPGA IP Signals

10.1. Native Floating Point DSP Intel® Agilex™ FPGA IP Release Information

10.2. Native Floating Point DSP Intel® Agilex™ FPGA IP Core Supported Operational Modes

10.3. Parameterizing the Native Floating Point DSP Intel® Agilex™ FPGA IP

10.4. Native Floating Point DSP Intel® Agilex™ FPGA IP Core Signals

10.4.1. FP32 Multiplication Mode Signals

10.4.2. FP32 Addition or Subtraction Mode Signals

10.4.3. FP32 Multiplication with Addition or Subtraction Mode Signals

10.4.4. FP32 Multiplication with Accumulation Mode Signals

10.4.5. FP32 Vector One and Vector Two Modes Signals

10.4.6. Sum of Two FP16 Multiplication Mode Signals

10.4.7. Sum of Two FP16 Multiplication with FP32 Addition Mode Signals

10.4.8. Sum of Two FP16 Multiplication with Accumulation Mode Signals

10.4.9. FP16 Vector One and Vector Two Modes Signals

10.4.10. FP16 Vector Three Mode Signals

Visible to Intel only — GUID: kly1462519667619

Ixiasoft

6.2.1.3. Pre-adder Input Mode

In this mode, one multiplier operand derives from the pre-adder, and the other operand derives from the datac[] input port.

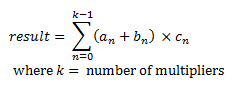

This mode is expressed in the following equation.

The following shows the pre-adder input mode of a multiplier.

Figure 60. Pre-adder Input Mode