Visible to Intel only — GUID: eha1677988944449

Ixiasoft

1. Overview

2. Getting Started

3. F-Tile Ethernet Intel® FPGA Hard IP Parameters

4. Functional Description

5. Clocks

6. Resets

7. Interface Overview

8. Configuration Registers

9. Supported Modules and IPs

10. Supported Tools

11. F-Tile Ethernet Intel® FPGA Hard IP User Guide Archives

12. Document Revision History for the F-Tile Ethernet Intel® FPGA Hard IP User Guide

4.4.1. Features

4.4.2. PTP Timestamp Accuracy

4.4.3. PTP Client Flow

4.4.4. RX Virtual Lane Offset Calculation for No FEC Variants

4.4.5. Virtual Lane Order and Offset Values

4.4.6. UI Adjustment

4.4.7. Reference Time Interval

4.4.8. Minimum and Maximum Reference Time (TAM) Interval for UI Measurement (Hardware)

4.4.9. UI Value and PMA Delay

4.4.10. Routing Delay Adjustment for Advanced Timestamp Accuracy Mode

4.4.11. Routing Delay Adjustment for Basic Timestamp Accuracy Mode

5.1. Clock Connections in Single Instance Operation

5.2. Clock Connections in Multiple Instance Operation

5.3. Clock Connections in MAC Asynchronous FIFO Operation

5.4. Clock Connections in PTP-Based Synchronous and Asynchronous Operation

5.5. Clock Connections in Synchronous Ethernet Operation

5.6. Custom Cadence

7.1. Status Interface

7.2. TX MAC Avalon ST Client Interface

7.3. RX MAC Avalon ST Aligned Client Interface

7.4. TX MAC Segmented Client Interface

7.5. RX MAC Segmented Client Interface

7.6. MAC Flow Control Interface

7.7. PCS Mode TX Interface

7.8. PCS Mode RX Interface

7.9. FlexE and OTN Mode TX Interface

7.10. FlexE and OTN Mode RX Interface

7.11. Custom Rate Interface

7.12. 32-bit Soft CWBIN Counters

7.13. Reconfiguration Interfaces

7.14. Precision Time Protocol Interface

7.2.1. TX MAC Avalon ST Client Interface with Disabled Preamble Passthrough

7.2.2. TX MAC Avalon ST Client Interface with Enabled Preamble Passthrough

7.2.3. Using MAC Avalon ST skip_crc Signal to Control Source Address, PAD, and CRC Insertion

7.2.4. Using MAC Avalon ST i_tx_error Signal to Mark Packets Invalid

7.4.1. TX MAC Segmented Client Interface with Disabled Preamble Passthrough

7.4.2. TX MAC Segmented Client Interface with Enabled Preamble Passthrough

7.4.3. Using MAC Segmented skip_crc Signal to Control Source Address, PAD, and CRC Insertion

7.4.4. Using MAC Segmented i_tx_mac_error to Mark Packets Invalid

Visible to Intel only — GUID: eha1677988944449

Ixiasoft

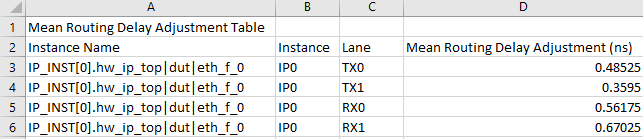

4.4.11. Routing Delay Adjustment for Basic Timestamp Accuracy Mode

Follow the steps below to generate the routing delay information and apply the delay information to the TX/RX TAM adjust calculations described in the PTP TX/RX Client Flow sections.

For hardware run with Timestamp accuracy mode set to Basic, use the eth_f_ptp_report_dl_path_delay.tcl script to generate the routing delay information.

The steps to execute .tcl script is same as advanced accuracy mode. For more information to execute .tcl scripts, refer to the steps 1 to 3 in the Routing Delay Adjustment for Advanced Timestamp Accuracy Mode.

- The generated TX and RX routing delay adjustment information is available in these views:

- In the Command Prompt window:

Info: PTP DL Path Routing delay adjustment summary: Info: Mean TX Routing delay adjustment for IP_INST[0].hw_ip_top|dut|eth_f_0 lane[0] = 0.48525 ns Info: Mean TX Routing delay adjustment for IP_INST[0].hw_ip_top|dut|eth_f_0 lane[1] = 0.3595 ns Info: Mean RX Routing delay adjustment for IP_INST[0].hw_ip_top|dut|eth_f_0 lane[0] = 0.56175 ns Info: Mean RX Routing delay adjustment for IP_INST[0].hw_ip_top|dut|eth_f_0 lane[1] = 0.67025 ns Info (23030): Evaluation of Tcl script eth_f_ptp_report_dl_path_delay.tcl was successful

- In the generated ptp_hw_basic_adj.tcl script:

#Mean Routing Delay Adjustment (ns) #IP0: IP_INST[0] hw_ip_top|dut|eth_f_0 set IP0_TX0_ROUTING_ADJ 0.48525 set IP0_TX1_ROUTING_ADJ 0.3595 set IP0_RX0_ROUTING_ADJ 0.56175 set IP0_RX1_ROUTING_ADJ 0.67025

- In ptp_hw_basic_adj.csv file:

- In the Command Prompt window:

- Use the generated routing delay values in the tx/rx_tam_adjust calculation specified in PTP TX Client Flow and PTP RX Client Flow.

Note: If you modify your project and rerun the compilation, you also must regenerate the routing delay information by following the steps above.