Visible to Intel only — GUID: rdy1614854421346

Ixiasoft

Visible to Intel only — GUID: rdy1614854421346

Ixiasoft

9.1.4. Parameters

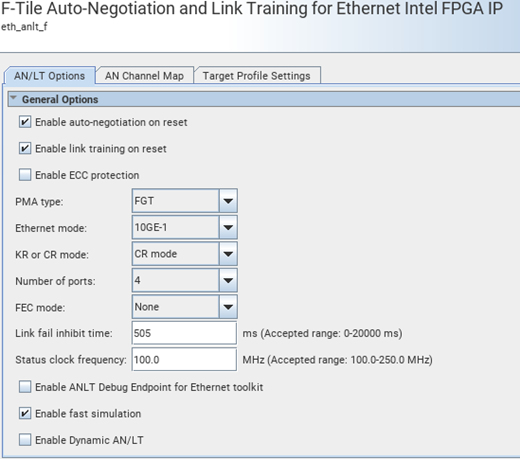

The F-Tile Auto-Negotiation and Link Training for Ethernet Intel® FPGA IP parameter editor provides the parameters you can set to configure your IP variation.

- AN/LT Options

- AN Channel Map

- Target Profile Settings

| Parameter |

Range |

Default Setting |

Parameter Description |

|---|---|---|---|

| Mode selection | |||

| Enable auto-negotiation on reset |

|

On | Enable Auto-negotiation. |

| Enable link training on reset |

|

On | Enable Link Training. |

| Enable ECC protection |

|

Off | Enable Error Correction Code (ECC) for Nios® II memory. To enable this feature, you must acquire Nios® II license. Contact Intel Sales for information about acquiring a license. |

| PMA type |

|

FGT | PMA Type. Selects the PMA type. Each PMA has a different data rate range and compliance specifications. The selected mode must match with PMA mode selected in Base IP. |

| Ethernet mode |

|

10GE-1 | Ethernet Configuration. Specifies the overall port bandwidth across the number of physical lanes used by the port. Term XGbE-Y represents:

The selected mode must match with Ethernet mode selected in Base IP. |

| KR or CR mode |

|

CR mode | Selects the option during auto-negotiation. |

| Number of ports | 1-16 | 4 | Selects number of base Ethernet IP ports connected to the IP. |

| FEC mode |

|

None | Selects the FEC mode for each port.

The IP core supports the following FEC types

|

| Link fail inhibit time | 0-20000 |

|

Sets the link fail inhibit timeout for auto-negotiation in milliseconds.

Default value:

|

| Status clock frequency | 100-250 | 100 | Selects the auto-negotiation and link training status clock frequency. Must be set to the frequency of the i_clk input for the correct timer functionality. |

| Enable ANLT Debug Endpoint for Ethernet Toolkit |

|

Off | Enables JTAG interface to external terminal so that Ethernet Tool Kit (ETK) can access the AN/LT configuration and status registers. |

| Enable Fast Simulation |

|

On | Enable fast simulation to skip auto-negotiation and link training functionality and FHT or FGT features. Additionally, it updates the AN/LT status registers to reflect AN/LT completion.

Note: Enable Fast Simulation is not supported when Enable Dynamic AN/LT is enabled.

|

| Enable Dynamic AN/LT |

|

Off | Enables the Dynamic reconfiguration feature for AN/LT IP. Make sure the correct combination of settings are used based on the base ethernet IP secondary profiles associated with the ANLT port. Selecting this parameter enables the Target Profile Settings tab.

Note: The Enable AN/LT you select depends on the base ethernet IP secondary profiles associated with the AN/LT port.

|

| AN Channel Map |

|||

| AN channel |

|||

| AN channel location <n> |

0-7 | 0 |

Selects the AN lane default location in each Ethernet ports. <n> is an integer from 0 to (number of lanes - 1). For example, for 100GE-4, AN channel location <n> parameter can be 0 to 3.

Note:

This option is not available for single lane (For example, 10GE-1, 25GE-1). |

|

Target Profile Settings

Note: Make sure the correct combination of settings are used based on the base ethernet IP secondary profiles associated with the ANLT port.

|

|||

| Advertise Low Latency FEC Request |

|

Off | Sets the value of the override consortium low-latency FEC request field, bit 3 of Register 0xCC. |

| Advertise RS-FEC Request |

|

Off | Must be set to the value of the override RS-FEC ability field, bit 10 of Register 0xCC. |

| Advertise RS-FEC Ability |

|

Off | Sets the value of the override RS-FEC ability field bit 8 of Register 0xCC. |

| Advertise BASER-FEC Request |

|

Off | Sets the value of the override BASER-FEC request field, bit 11 of Register 0xCC. |

| Advertise BASER-FEC Ability |

|

Off | Sets the value of the override BASER-FEC ability field, bit 9 of Register 0xCC. |

| Advertise Low Latency FEC Ability |

|||

| LL FEC Ability for 50G BASE-CR1/KR1 |

|

Off | Sets the value of the override consortium low-latency FEC ability field, bit 4 of Register 0xCC. |

| LL FEC Ability for 100G BASE-CR2/KR2 |

|

Off | Sets the value of the override consortium low-latency FEC ability field, bit 5 of Register 0xCC. |

| LL FEC Ability for 200G BASE-CR4/KR4 |

|

Off | Sets the value of the override consortium low-latency FEC ability field, bit 6 of Register 0xCC. |

| Advertise IEEE Port Ability | |||

| 10G BASE-KR(A2) |

|

Off | Sets the value of the override IEEE port ability fields, bit 12 of Register 0xCC. |

| 40G BASE-KR4 (A3) |

|

Off | Sets the value of the override IEEE port ability fields, bit 13 of Register 0xCC. |

| 40G BASE-CR4 (A4) |

|

Off | Sets the value of the override IEEE port ability fields, bit 14 of Register 0xCC. |

| 100G BASE-KR4(A7) |

|

Off | Sets the value of the override IEEE port ability fields, bit 15 of Register 0xCC. |

| 100G BASE-CR4(A8) |

|

Off | Sets the value of the override IEEE port ability fields, bit 16 of Register 0xCC. |

| 25G BASE-KR-S/CR-S/A9 |

|

Off | Sets the value of the override IEEE port ability fields, bit 17 of Register 0xCC. |

| 25G BASE-KR-CR-A10 |

|

Off | Sets the value of the override IEEE port ability fields, bit 18 of Register 0xCC. |

| 50G BASE-KR-CR(A13) |

|

Off | Sets the value of the override IEEE port ability fields Bit 19 of Register 0xCC. |

| 100G BASE-KR2/CR2(A14) |

|

Off | Sets the value of the override IEEE port ability fields, bit 20 of Register 0xCC. |

| 200G BASE-KR/CR4(A15) |

|

Off | Sets the value of the override IEEE port ability fields, bit 21 of Register 0xCC. |

| 100G BASE-KR/CR(A16) |

|

Off | Sets the value of the override IEEE port ability fields, bit 22 of Register 0xCC. |

| 200G BASE -KR2/CR2 (A17) |

|

Off | Sets the value of the override IEEE port ability fields,bit 23 of Register 0xCC. |

| 400G BASE - KR4/CR4 |

|

Off | Sets the value of the override IEEE port ability fields, bit 29 of Register 0xCC. |

| Advertise Consortium Port Ability | |||

| 25G BASE-KR1 (D20) |

|

Off | Sets the value of the override consortium port ability fields, bit 24 of Register 0xCC. |

| 25G BASE-CR1 (D21) |

|

Off | Sets the value of the override consortium port ability fields, bit 25 of Register 0xCC. |

| 50 BASE-KR2 (D24) |

|

Off | Sets the value of the override consortium port ability fields,bit 26 of Register 0xCC. |

| 50 BASE-CR2 (D25) |

|

Off | Sets the value of the override consortium port ability fields, bit 27 of Register 0xCC. |

| 400G BASR-KR8/CR8 (D34) |

|

Off | Sets the value of the override consortium port ability fields, bit 28 of Register 0xCC. |