Visible to Intel only — GUID: zlo1707232568238

Ixiasoft

4.1. Remote Interface Signals

4.2. I/O PLL Interface Signals

4.3. Status Interface Signals

4.4. Global CSR interface Signals

4.5. Memory AXI4 Driver Interface Signals

4.6. CSR AXI-Lite Driver Interface Signals

4.7. Memory Status Driver Interface Signals

4.8. Memory Reset Driver Interface Signals

4.9. CAM AXI-Stream Driver Interface Signals

4.10. Registers

4.10.1.1. version_0

4.10.1.2. version_1

4.10.1.3. ctrl_status_0

4.10.1.4. driver_ctrl_status_1

4.10.1.5. driver_run_bitmask_0

4.10.1.6. driver_run_bitmask_1

4.10.1.7. driver_run_bitmask_2

4.10.1.8. driver_run_bitmask3

4.10.1.9. driver_done_bitmask_0

4.10.1.10. driver_done_bitmask_1

4.10.1.11. driver_done_bitmask_2

4.10.1.12. driver_done_bitmask_3

4.10.1.13. driver_error_bitmask_0

4.10.1.14. driver_error_bitmask_1

4.10.1.15. driver_error_bitmask_2

4.10.1.16. driver_error_bitmask_3

4.10.2.1. version_lo

4.10.2.2. version_hi

4.10.2.3. ctrl_stat_lo

4.10.2.4. ctrl_stat_hi

4.10.2.5. scratchpad_lo

4.10.2.6. scratchpad_hi

4.10.2.7. wr_log_ram_stat_lo

4.10.2.8. wr_log_ram_stat_hi

4.10.2.9. wr_log_ram_ctrl_lo

4.10.2.10. wr_log_ram_ctrl_hi

4.10.2.11. rd_log_ram_stat_lo

4.10.2.12. rd_log_ram_stat_hi

4.10.2.13. rd_log_ram_ctrl_lo

4.10.2.14. rd_log_ram_ctrl_hi

4.10.2.15. wr_err_counters_0_lo

4.10.2.16. wr_err_counters_0_hi

4.10.2.17. rd_err_counters_0_lo

4.10.2.18. rd_err_counters_0_hi

4.10.2.19. rd_err_counters_1_lo

4.10.2.20. rd_err_counters_1_hi

4.10.2.21. rd_pnf_0_lo

4.10.2.22. rd_pnf_0_hi

4.10.2.23. rd_pnf_1_lo

4.10.2.24. rd_pnf_1_hi

4.10.2.25. rd_pnf_2_lo

4.10.2.26. rd_pnf_2_hi

4.10.2.27. rd_pnf_3_lo

4.10.2.28. rd_pnf_3_hi

4.10.2.29. rd_pnf_4_lo

4.10.2.30. rd_pnf_4_hi

4.10.2.31. rd_pnf_5_lo

4.10.2.32. rd_pnf_5_hi

4.10.2.33. rd_pnf_6_lo

4.10.2.34. rd_pnf_6_hi

4.10.2.35. rd_pnf_7_lo

4.10.2.36. rd_pnf_7_hi

4.10.2.37. rd_pnf_8_lo

4.10.2.38. rd_pnf_8_hi

4.10.2.39. rd_pnf_9_lo

4.10.2.40. rd_pnf_9_hi

4.10.2.41. rd_pnf_10_lo

4.10.2.42. rd_pnf_10_hi

4.10.2.43. rd_pnf_11_lo

4.10.2.44. rd_pnf_11_hi

4.10.2.45. rd_pnf_12_lo

4.10.2.46. rd_pnf_12_hi

4.10.2.47. rd_pnf_13_lo

4.10.2.48. rd_pnf_13_hi

4.10.2.49. rd_pnf_14_lo

4.10.2.50. rd_pnf_14_hi

4.10.2.51. rd_pnf_15_lo

4.10.2.52. rd_pnf_15_hi

4.10.2.53. rd_pnf_16_lo

4.10.2.54. rd_pnf_16_hi

4.10.2.55. rd_pnf_17_lo

4.10.2.56. rd_pnf_17_hi

4.10.2.57. rd_pnf_18_lo

4.10.2.58. rd_pnf_18_hi

4.10.2.59. rd_pnf_19_lo

4.10.2.60. rd_pnf_19_hi

4.10.2.61. ter_dq_mask_0_lo

4.10.2.62. ter_dq_mask_0_hi

4.10.2.63. ter_dq_mask_1_lo

4.10.2.64. ter_dq_mask_1_hi

4.10.2.65. ter_lo

4.10.2.66. ter_hi

5.2.2.1. dq_alu_echo_op

5.2.2.2. dq_alu_invert_op

5.2.2.3. dq_alu_rotate_op

5.2.2.4. dq_alu_prbs_op

5.2.2.5. data_eq_dq_op

5.2.2.6. data_eq_raw_op

5.2.2.7. data_eq_addr_op

5.2.2.8. data_eq_id_op

5.2.2.9. dm_alu_echo_op

5.2.2.10. dm_alu_invert_op

5.2.2.11. dm_alu_rotate_op

5.2.2.12. dm_alu_prbs_op

5.2.2.13. strb_eq_dm_op

5.2.2.14. strb_eq_raw_op

5.2.2.15. addr_alu_echo_op

5.2.2.16. addr_alu_incr_op

5.2.2.17. addr_alu_rand_op

5.2.2.18. addr_op

5.2.2.19. write_worker_op

5.2.2.20. read_worker_op

5.2.2.21. write_cmd

5.2.2.22. read_cmd

5.2.2.23. wait_writes_cmd

5.2.2.24. wait_reads_cmd

5.2.2.25. sleep_cmd

5.2.2.26. driver_post_cmd

5.2.2.27. driver_wait_cmd

5.2.2.28. parallel_cmd

5.2.2.29. loop_cmd

Visible to Intel only — GUID: zlo1707232568238

Ixiasoft

2. Test Engine IP - Introduction

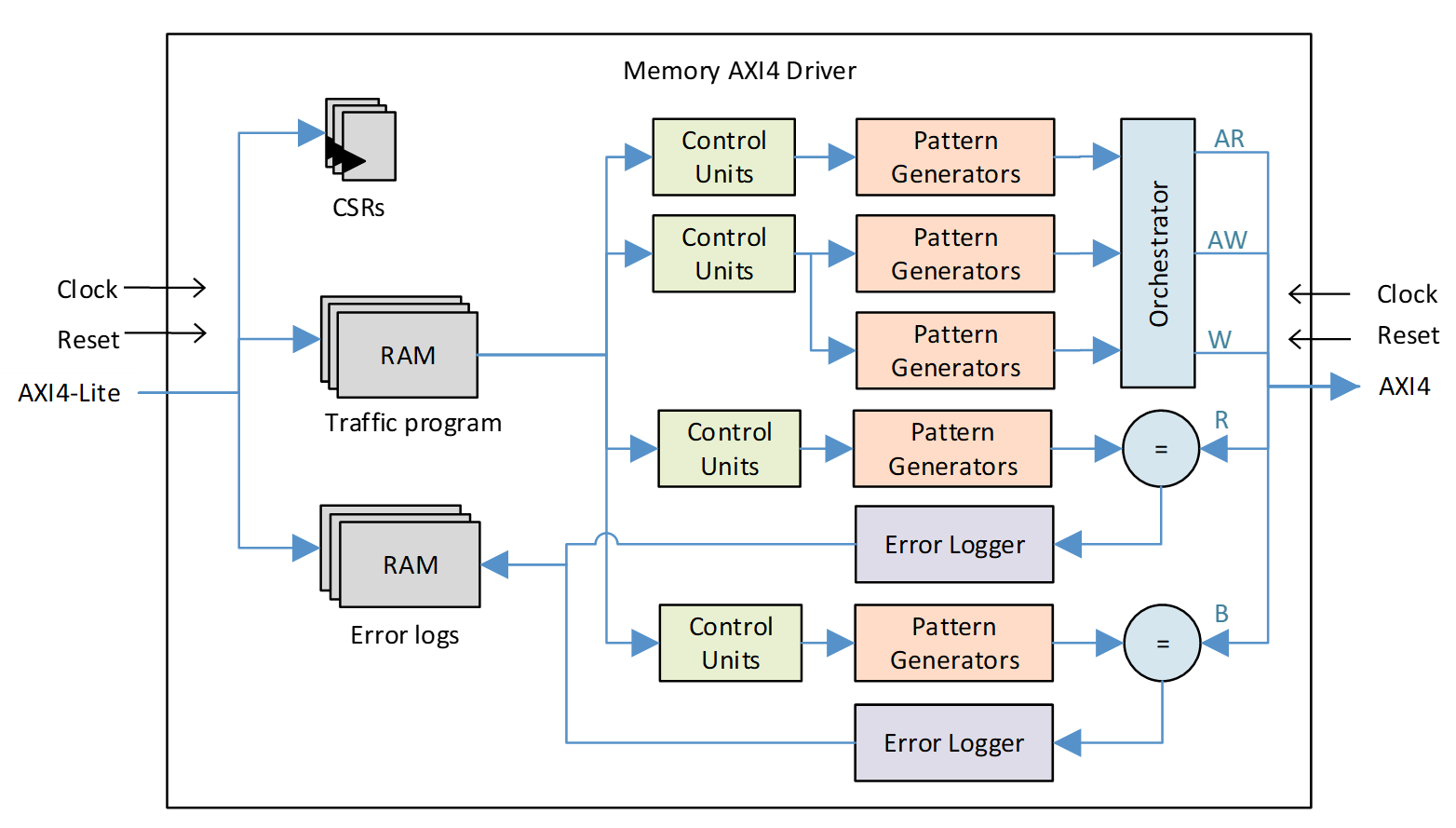

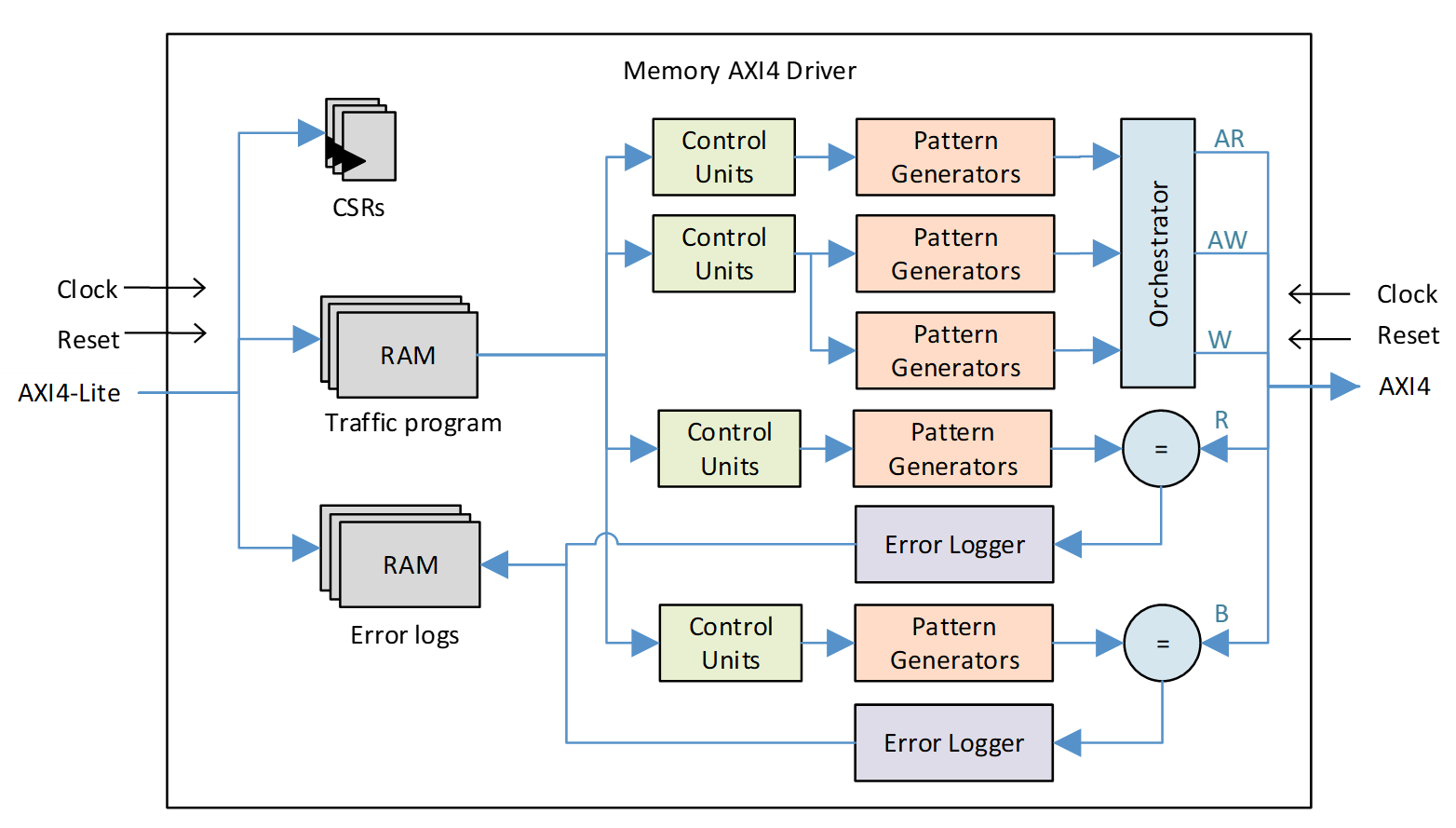

The Test Engine IP is a software-programmable AXI traffic generator that generates a configurable pattern of reads and writes to a programmable memory address range.

You can use the Test Engine IP to access multiple AXI interfaces and exercise the generated configurable patterns. This AXI traffic generator also monitors the data read from the memory to ensure that it matches the expected data; if the read data doesn't match the expected data, the Test Engine IP asserts a failure. All failures are captured within the error logs.

Figure 1. Test Engine IP's Memory AXI4 Driver Architecture