Visible to Intel only — GUID: ofn1705621413910

Ixiasoft

1.2. Generating the Design

Procedure

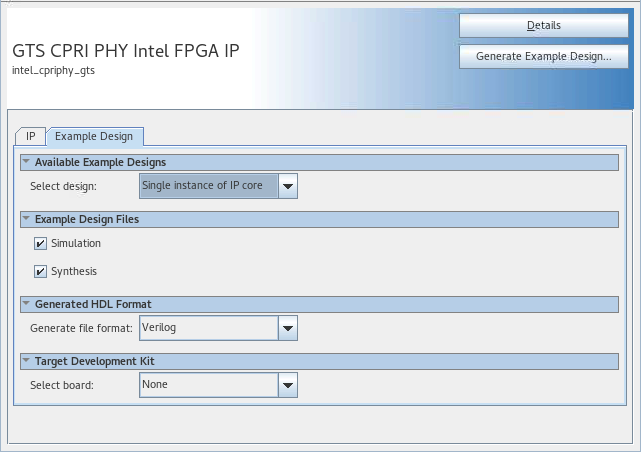

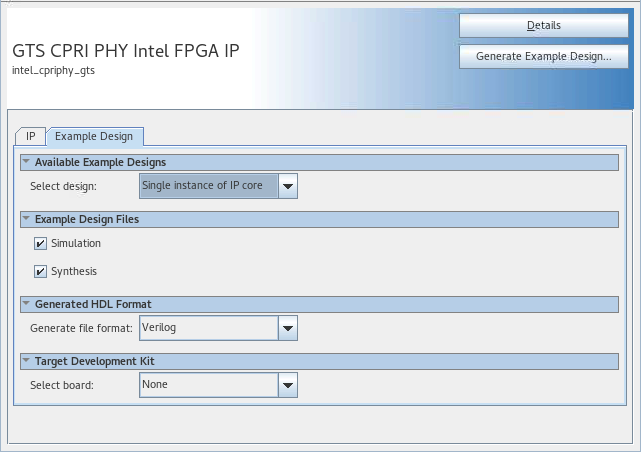

Example Design Tab in IP Parameter Editor

To create an Quartus® Prime Pro Edition project:

- In the Quartus® Prime Pro Edition software, click File > New Project Wizard to create a new project, or File > Open Project to open an existing project. The wizard prompts you to specify a device.

- Specify the device family Agilex™ 5 (E-series/D-series) and select a device that meets all of these requirements:

- Transceiver tile: GTS

- Transceiver speed grade: -1 or 0

- Core speed grade: -1 or -2 or -3 or -4

- Click Finish.

Follow these steps to generate the GTS CPRI PHY Intel® FPGA IP hardware design example and testbench:

- In the IP Catalog, locate and select GTS CPRI PHY Intel® FPGA IP. The New IP Variation dialog box appears.

- Specify a top-level name for your custom IP variation. The parameter editor saves the IP variation settings in a file named <your_ip> .ip.

- Click OK. The parameter editor appears.

- On the IP tab, specify the parameters for your IP core variation.

- On the Example Design tab, under Example Design Files, select the Simulation option to generate the testbench and the compilation-only project. Select the Synthesis option to generate the hardware design example. You must select at least one of the Simulation and Synthesis options to generate the design example.

- On the Example Design tab, under Generated HDL Format, select Verilog HDL or VHDL. If you select VHDL, you must simulate the testbench with a mixed-language simulator. The device under test in the ex_<datarate> directory is a VHDL model, but the main testbench file is a SystemVerilog file.

- Click the Generate Example Design button. The Select Example Design Directory dialog box appears.

- If you want to modify the design example directory path or name from the defaults (intel_cpriphy_gts_0_example_design), browse to the new path and type the new design example directory name (<design_example_dir>).