Visible to Intel only — GUID: scm1677254495017

Ixiasoft

Visible to Intel only — GUID: scm1677254495017

Ixiasoft

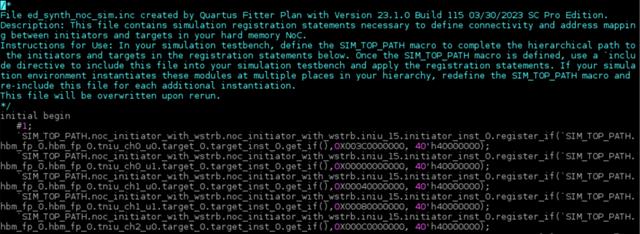

6.3. Contents of Simulation Registration Include File

The simulation registration include file generates into your project directory, in Verilog HDL format, with the name <top_module>_noc_sim.inc. This simulation registration include file has all the necessary registration information for each initiator-to-target connection using a SIM_TOP_PATH macro to specify the hierarchical path.

To use this file, edit your top-level simulation testbench to define the SIM_TOP_PATH macro to complete the hierarchical path to the initiators and targets relative to the testbench.

Once you define the SIM_TOP_PATH macro, use the `include directive to include this file into your simulation testbench and apply the registration statements. If your simulation environment instantiates these modules at multiple places in your hierarchy, redefine the SIM_TOP_PATH macro and re-include this file for each additional instantiation. Do not edit the simulation registration include file directly because the Compiler rewrites this file during each compilation.

The format for the registration statements in Verilog HDL is as follows. Use the Verilog HDL hierarchy delimiter, ., instead of the Intel® Quartus® Prime hierarchy delimiter, |. Also, express hexadecimal numbers using Verilog HDL format.

<hierarchical initiator path name>.register_if\

(<hierarchical target path name>.get_if(),\

<hexadecimal base address>, \

<hexadecimal span of memory>);

For example, the following registration statement specifies a connection with a base address of 0 and spanning 40000000 (hexadecimal) addresses:

`SIM_TOP_PATH.noc_init|noc_init|iniu_0|initiator_inst_ 0.register_if(`SIM_TOP_PATH.noc_hbm|noc_hbm|tniu_ch0_u0|target_0.target_inst_0.get_if(), 44'h0, 44'h40000000);

/* File test_noc_sim.inc created by Quartus Version 23.3.0 Internal Build 81 08/20/2023 SC Pro Edition. Description: This file contains simulation registration statements necessary to define connectivity and address mapping between initiators and targets in your hard memory NoC. Instructions for Use: In your simulation testbench, define the SIM_TOP_PATH macro to complete the hierarchical path to the initiators and targets in the registration statements below. Once the SIM_TOP_PATH macro is defined, use a `include directive to include this file into your simulation testbench and apply the registration statements. If your simulation environment instantiates these modules at multiple places in your hierarchy, redefine the SIM_TOP_PATH macro and re-include this file for each additional instantiation. This file will be overwritten upon rerun. */ initial begin #1; `SIM_TOP_PATH.noc_init|noc_init|iniu_0|initiator_inst_ 0.register_if(`SIM_TOP_PATH.noc_hbm|noc_hbm|tniu_ch0_ch1_sb|target_0.target_lite_inst_0.get_if(), 44'h80000000, 44'h8000000); `SIM_TOP_PATH.noc_init|noc_init|iniu_0|initiator_inst_ 0.register_if(`SIM_TOP_PATH.noc_hbm|noc_hbm|tniu_ch0_u0|target_0.target_inst_0.get_if(), 44'h0, 44'h40000000); `SIM_TOP_PATH.noc_init|noc_init|iniu_0|initiator_inst_ 0.register_if(`SIM_TOP_PATH.noc_hbm|noc_hbm|tniu_ch0_u1|target_0.target_inst_0.get_if(), 44'h40000000, 44'h40000000); `SIM_TOP_PATH.noc_init|noc_init|iniu_1|initiator_inst_ 0.register_if(`SIM_TOP_PATH.noc_hbm|noc_hbm|tniu_ch0_u0|target_0.target_inst_0.get_if(), 44'h0, 44'h40000000); `SIM_TOP_PATH.noc_init|noc_init|iniu_1|initiator_inst_ 0.register_if(`SIM_TOP_PATH.noc_hbm|noc_hbm|tniu_ch0_u1|target_0.target_inst_0.get_if(), 44'h40000000, 44'h40000000); end