Visible to Intel only — GUID: kdh1662365530901

Ixiasoft

1. Quick Start Guide

2. F-Tile 25G Ethernet Single-Channel Design Example

3. F-Tile 25G Ethernet Single Channel Design Example with Dynamic Reconfiguration

4. F-Tile 25G Ethernet Intel FPGA IP Design Example User Guide Archives

5. Document Revision History for F-Tile 25G Ethernet Intel® FPGA IP Design Example User Guide

1.1. Directory Structure

1.2. Generating the Design Example

1.3. Generating Tile Files

1.4. Simulating the F-Tile 25G Ethernet Intel FPGA IP Design Example Testbench

1.5. Compiling and Configuring the Design Example in Hardware

1.6. Testing the F-Tile 25G Ethernet Intel FPGA IP Hardware Design Example

Visible to Intel only — GUID: kdh1662365530901

Ixiasoft

2.6.1. Test Procedure

Follow these steps to test the design example in hardware:

- In the system console, navigate to the hwtest folder and run the command: source main.tcl to select a JTAG master. By default, the first JTAG master on the JTAG chain is selected. To select the JTAG master for Intel Agilex® 7 devices, run this command: set_jtag <number of appropriate JTAG master>. Example: set_jtag 1.

- Run the following commands in the system console to start the serial loopback test:

Table 7. Command Parameters Parameter Description Example Usage chkphy_status <link num> Displays the clock frequencies and PHY lock status. % chkphy_status 0 # Check status of link 0 chkmac_stats <link num> Displays the values in the MAC statistics counters. % chkmac_stats 0 # Checks mac statistics counter of link 0 clear_all_stats <link num> Clears the IP core statistics counters. % clear_all_stats 0 # Clears statistics counter of link 0 start_gen <link num> Starts the packet generator. % start_gen 0 # Begin packet generation on link 0 stop_gen <link num> Stops the packet generator. % stop_gen 0 # Stop packet generation on link 0 loop_on <link num> Turns on internal serial loopback. % loop_on 0 # Turn on internal loopback on link 0 loop_off <link num> Turns off internal serial loopback. % loop_off 0 # Turn off internal loopback on link 0 reg_read <addr> Returns the IP core register value at <addr>. % reg_read 0x402 # Read IP CSR register at address 402 of link 0 reg_write <addr> <data> Writes <data> to the IP core register at address <addr>. % reg_write 0x401 0x1 # Write 0x1 to IP CSR scratch register at address 401 of link 0 - Type loop_on <link num> to turn on the internal serial loopback mode.

- Type chkphy_status <link num> to check the status of the PHY. The TXCLK, RXCLK, and RX status should have the same values shown below for a stable link:

Link: 0 Addr: 100 RX PHY Register Access: Checking Clock Frequencies (KHz) TXCLK :39062 (KHZ) RXCLK :39063 (KHz) Link: 0 Addr: 100 RX PHY Status Polling Rx Frame Error 0x00000000 Tx PLL Lock Status 0x00000001 Rx Frequency Lock Status 0x00000001 RX PCS Ready 0x1 TX Lanes Stable 0x1 Deskewed Status 0x0 Link Fault Status 0x00000000 - Type clear_all_stats <link num> to clear TX and RX statistics registers.

- Type start_gen <link num> to begin packet generation.

- Type stop_gen <link num> to stop packet generation.

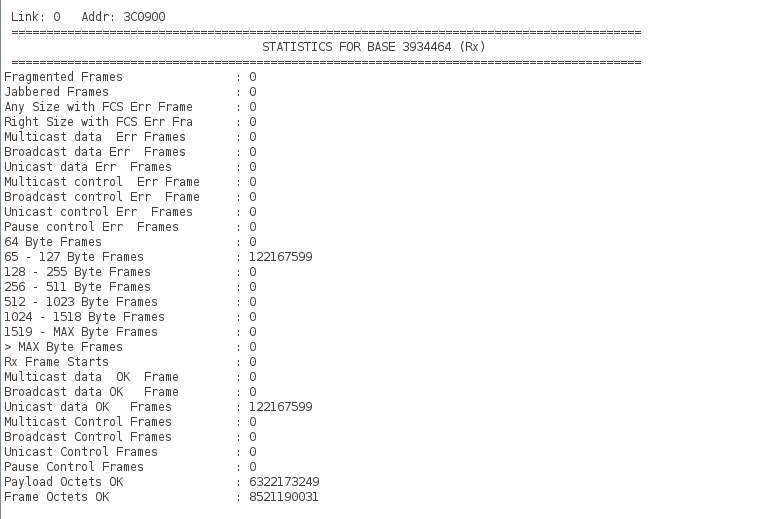

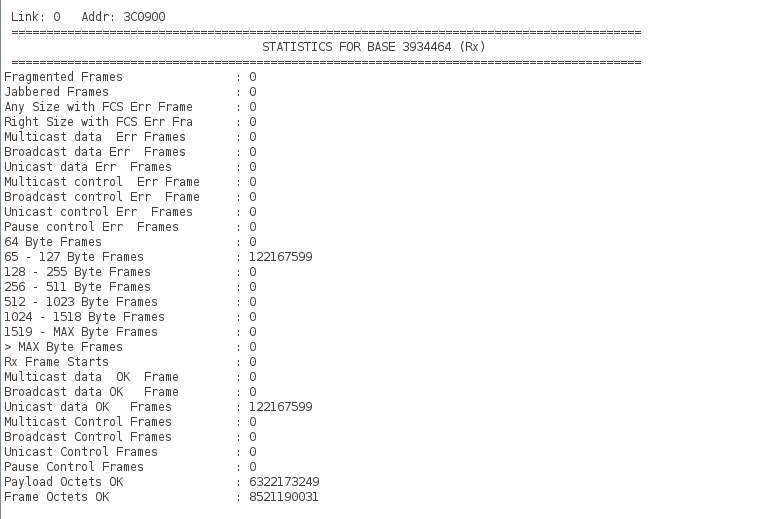

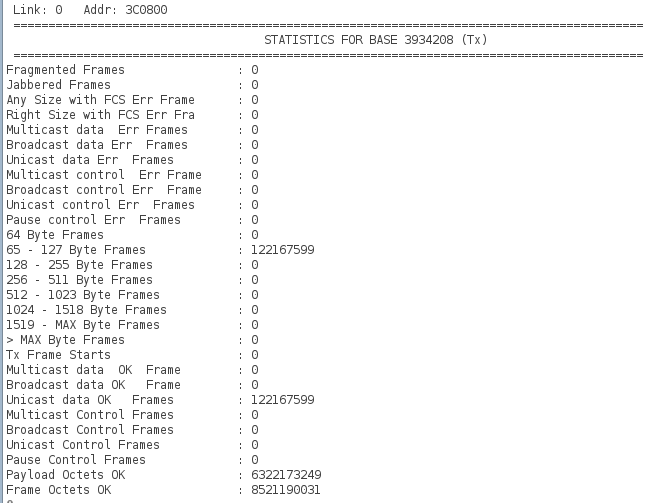

- Type chkmac_stats <link num> to read the TX and RX statistics counters. Make sure that:

- The transmitted packet frames match the received packet frames.

- No error frames are received.

- Type loop_off <link num> to turn off the internal serial loopback.

Figure 7. Sample Test Output—TX and RX Statistics Counters