Visible to Intel only — GUID: qvn1697528136096

Ixiasoft

1. Quick Start Guide

2. F-Tile 25G Ethernet Single-Channel Design Example

3. F-Tile 25G Ethernet Single Channel Design Example with Dynamic Reconfiguration

4. F-Tile 25G Ethernet Intel FPGA IP Design Example User Guide Archives

5. Document Revision History for F-Tile 25G Ethernet Intel® FPGA IP Design Example User Guide

1.1. Directory Structure

1.2. Generating the Design Example

1.3. Generating Tile Files

1.4. Simulating the F-Tile 25G Ethernet Intel FPGA IP Design Example Testbench

1.5. Compiling and Configuring the Design Example in Hardware

1.6. Testing the F-Tile 25G Ethernet Intel FPGA IP Hardware Design Example

Visible to Intel only — GUID: qvn1697528136096

Ixiasoft

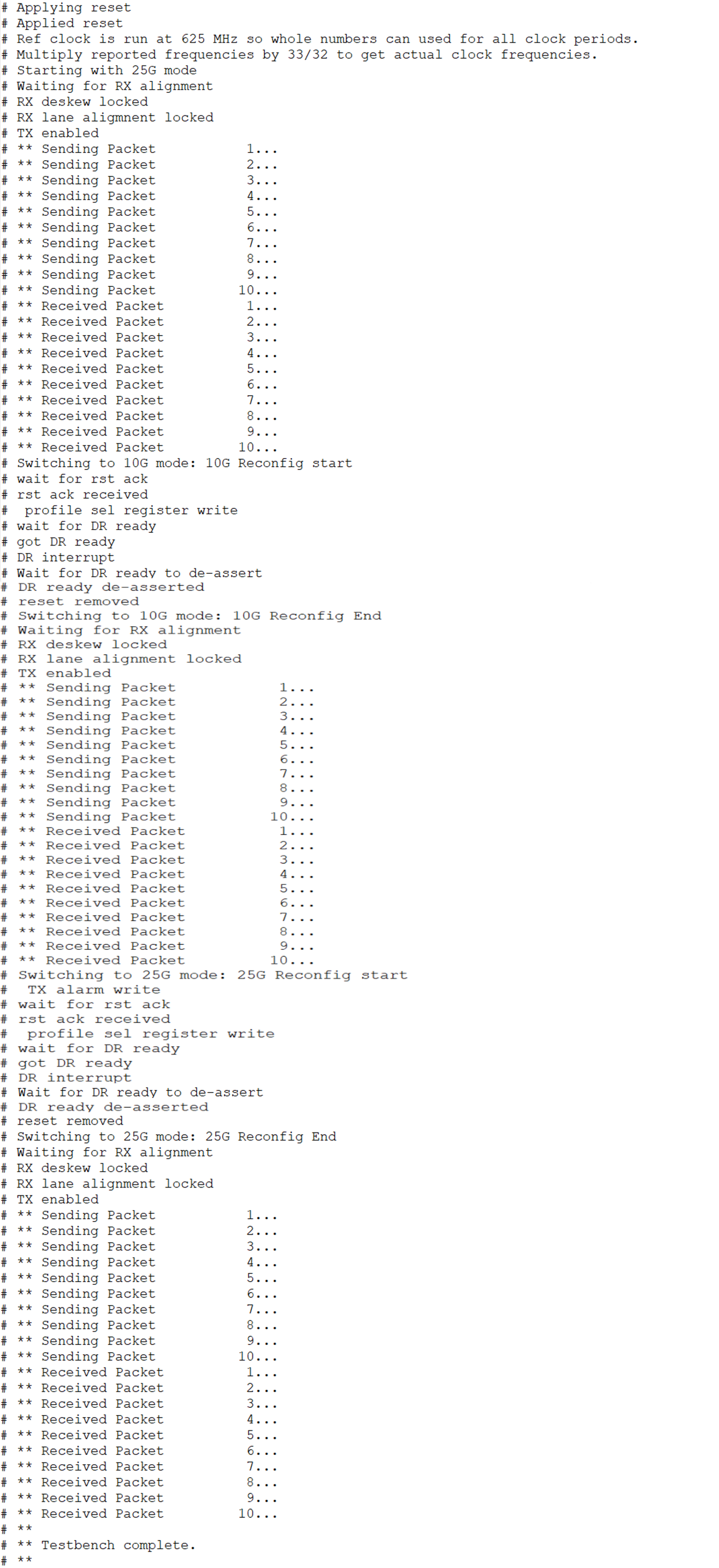

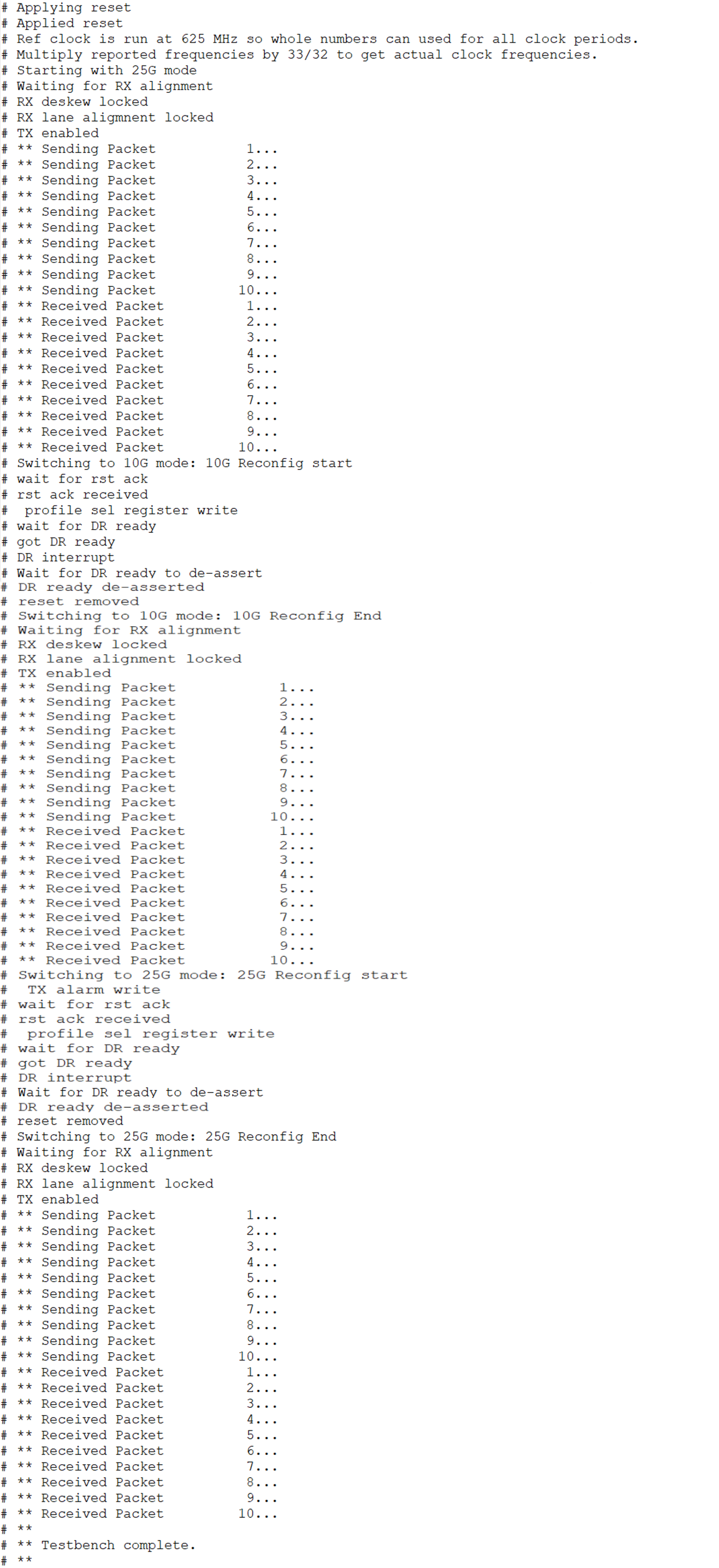

3.4.3. Test Case—Single-Channel Design Example with Dynamic Reconfiguration

The simulation test case performs the following actions:

- Instantiates F-Tile 25G Ethernet Intel® FPGA IP, dynamic reconfiguration controller, and SYS PLL.

- Starts up the design example with an operation speed of 25G.

- Waits for RX clock and RX alignment to settle.

- Transmits and receives 10 valid 64-bit data on 25G speed.

- The testbench performs the dynamic reconfiguration operation to switch the speed to 10G.

- Waits for RX clock and RX alignment to settle.

- Transmits and receives 10 valid 64-bit data on 10G speed.

- The testbench performs the dynamic reconfiguration operation to switch the speed back to 25G.

- Waits for RX clock and RX alignment to settle.

- Transmits and receives 10 valid 64-bit data on 25G speed.

- The successful testbench displays "Testbench complete.".

The following sample output illustrates a successful simulation test run: