Visible to Intel only — GUID: cln1638492615362

Ixiasoft

1. About this Document

2. Introduction

3. Nios® V Processor Hardware System Design with Intel® Quartus® Prime Pro Edition and Platform Designer

4. Nios® V Processor Software System Design

5. Nios® V Processor Configuration and Booting Solutions

6. Nios® V Processor - Using the MicroC/TCP-IP Stack

7. Nios® V Processor Debugging, Verifying, and Simulating

8. Document Revision History for the Nios® V Embedded Processor Design Handbook

5.1. Introduction

5.2. Linking Applications

5.3. Nios® V Processor Booting Methods

5.4. Introduction to Nios® V Processor Booting Methods

5.5. Nios® V Processor Booting from Configuration QSPI Flash

5.6. Nios V Processor Booting from On-Chip Memory (OCRAM)

5.7. Summary of Nios V Processor Vector Configuration and BSP Settings

7.4.1. Prerequisites

7.4.2. Setting Up and Generating Your Simulation Environment in Platform Designer

7.4.3. Creating Nios V Processor Software

7.4.4. Generating Memory Initialization File

7.4.5. Generating System Simulation Files

7.4.6. Running Simulation in the QuestaSim Simulator Using Command Line

Visible to Intel only — GUID: cln1638492615362

Ixiasoft

5.5.1.2.1. Hardware Design Flow

The following sections describe a step-by-step method for building a bootable system for a Nios V processor application copied from configuration QSPI flash to RAM using GSFI Bootloader. The following example is built using Intel Arria 10 SoC Development Kit.

IP Component Settings

- Create your Nios® V processor project using Intel® Quartus® Prime and Platform Designer.

- Add the Generic Serial Flash Interface Intel FPGA IP is into your Platform Designer system.

Figure 31. Connections for Nios V Processor ProjectFigure 32. Generic Serial Flash Interface Intel FPGA IP Parameter Settings

- Change the Device Density (Mb) according to the QSPI flash size.

- Change the addressing mode by modifying bit 8 of the Control Register value in the Default Settings parameter section. Changing bit 8 to 0x0 enables 3-byte addressing, or 0x1 enables 4-byte addressing

Note: Refer to Intel Supported Configuration Devices tab > Intel Supported Third Party Configuration Devices in Device Configuration Support Center to check the byte addressing mode supported for each flash device in each Intel FPGA device.

For example, Intel® Arria® 10 devices when used with Micron flash devices support the 4-byte addressing mode.

Reset and Exception Agent Settings for Nios Processor

- In the Nios V Processor parameter editor, set the Reset Agent to Bootloader ROM and Exception Agent to Exception RAM.

Figure 33. Nios V Parameter Editor Settings

- Click Generate HDL, the Generation dialog box appears.

- Specify output file generation options and then click Generate.

Intel Quartus Prime Software Settings

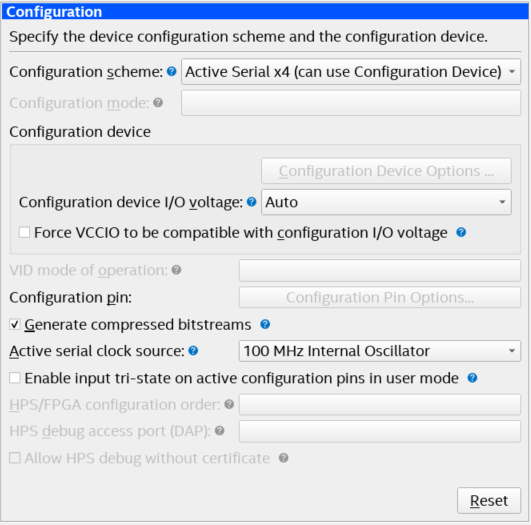

- In the Intel Quartus Prime software, click Assignment > Device > Device and Pin Options > Configuration .

- Set Configuration scheme to Active Serial x4 (can use Configuration Device).

- Set VID mode of operation according to your board design.

- Set the Active serial clock source to 100 MHz Internal Oscillator.

Figure 34. Device and Pin Options

- Click OK to exit the Device and Pin Options window.

- Click OK to exit the Device window.

- Click Start Compilation to compile your project.

Related Information