Visible to Intel only — GUID: fpo1634813159497

Ixiasoft

1. About the Fronthaul Compression Intel® FPGA IP

2. Getting Started with the Fronthaul Compression Intel® FPGA IP

3. Fronthaul Compression IP Functional Description

4. Fronthaul Compression IP Registers

5. Fronthaul Compression Intel FPGA IPs User Guide Archive

6. Document Revision History for the Fronthaul Compression Intel® FPGA IP User Guide

Visible to Intel only — GUID: fpo1634813159497

Ixiasoft

2.2. Parameterizing the Fronthaul Compression IP

Quickly configure your custom IP variation in the IP Parameter Editor.

- Create an Quartus® Prime Pro Edition project in which to integrate your IP core.

- In the Quartus® Prime Pro Edition, click File > New Project Wizard to create a new Intel Quartus Prime project, or File > Open Project to open an existing Quartus Prime project. The wizard prompts you to specify a device.

- Specify the device family that meets the speed grade requirements for the IP.

- Click Finish.

- In the IP Catalog, select Fronthaul Compression Intel FPGA IP.

The New IP Variation window appears.

- Specify a top-level name for your new custom IP variation.

The parameter editor saves the IP variation settings in a file named <your_ip> .ip.

- Click OK. The parameter editor appears.

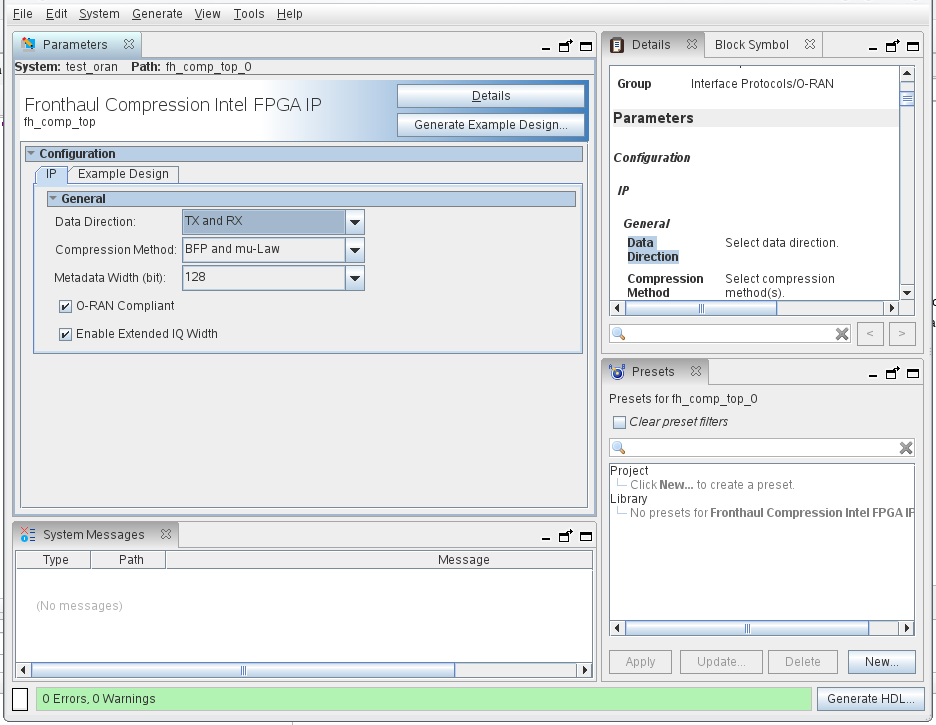

Figure 2. Fronthaul Compression IP Parameter Editor

- Specify the parameters for your IP variation. Refer to Parameters for information about specific IP parameters.

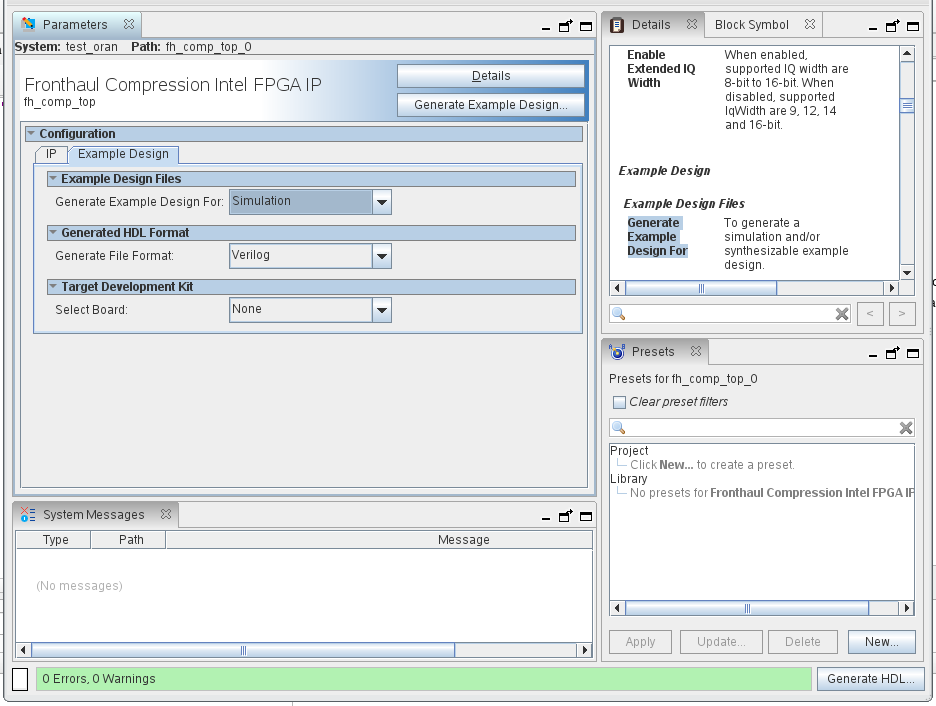

- Click the Design Example tab and specify the parameters for your design example.

Figure 3. Design Example Parameter Editor

- Click Generate HDL.

The Generation dialog box appears.

- Specify output file generation options, and then click Generate.

The IP variation files generate according to your specifications.

- Click Finish. The parameter editor adds the top-level .ip file to the current project automatically. If you are prompted to manually add the .ip file to the project, click Project > Add/Remove Files in Project to add the file.

- After generating and instantiating your IP variation, make appropriate pin assignments to connect ports and set any appropriate per-instance RTL parameters.