Multi Channel DMA Intel® FPGA IP for PCI Express* User Guide

A newer version of this document is available. Customers should click here to go to the newest version.

Visible to Intel only — GUID: gdl1589416831447

Ixiasoft

Visible to Intel only — GUID: gdl1589416831447

Ixiasoft

7.1. Generating the IP Core

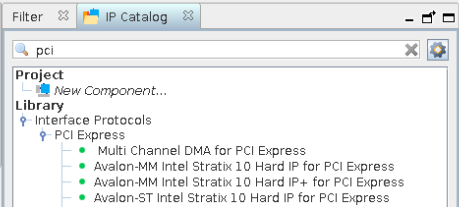

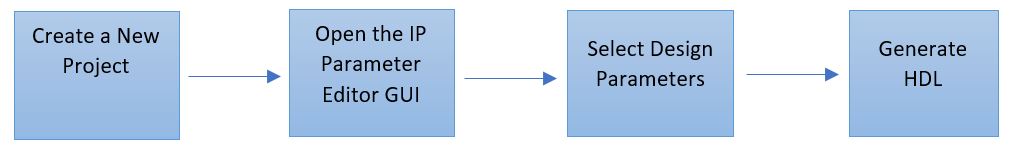

You can use the Intel® Quartus® Prime Pro Edition IP Catalog or Platform Designer to define and generate a Multi Channel DMA IP for PCI Express custom component.

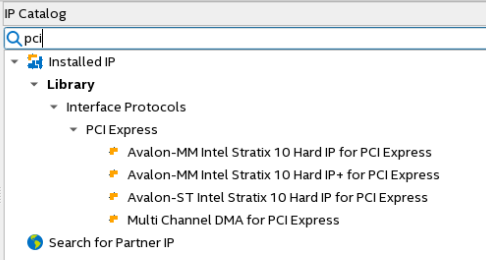

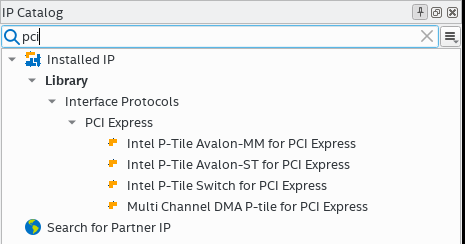

You can select Multi Channel DMA IP for PCI Express in the Intel® Quartus® Prime Pro Edition IP Catalog or Platform Designer as shown below.