Visible to Intel only — GUID: ula1593219899765

Ixiasoft

Visible to Intel only — GUID: ula1593219899765

Ixiasoft

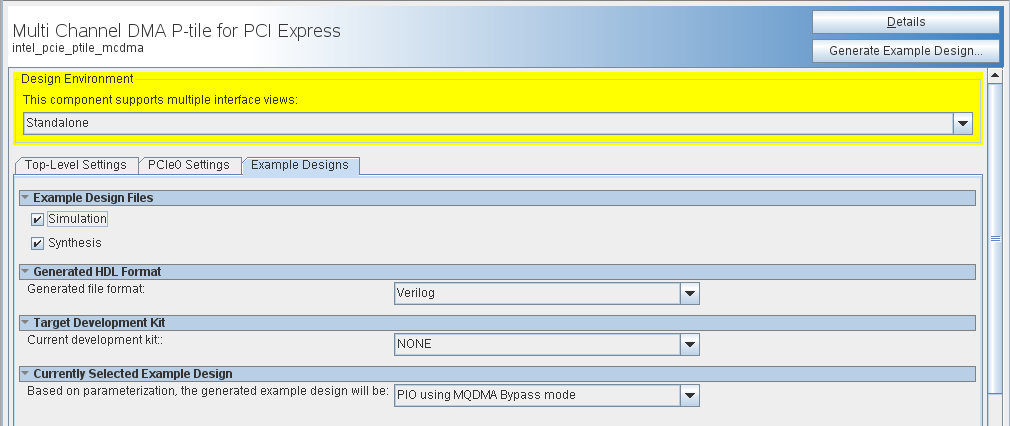

6.3. Example Designs

| Parameter | Value | Default Value | Description |

|---|---|---|---|

| Simulation |

On / Off |

True |

When Simulation box is checked, all necessary filesets required for simulation are generated. When this box is NOT checked, filesets required for Simulation are NOT generated. Instead a Qsys example design system is generated.

Note: Multiple physical functions and SR-IOV are not supported for simulation. When you generate an example design, turn off Simulation.

|

| Synthesis |

On / Off |

True |

When Synthesis box is checked, all necessary filesets required for synthesis are generated. When Synthesis box is NOT checked, filesets required for Synthesis are NOT generated. Instead a Qsys example design system is generated |

| Generated file format |

Verilog |

Verilog |

HDL format |

| Current development kit |

None Intel® Stratix® 10 DX P-Tile ES 1 FPGA Development Kit Intel® Agilex™ F-Series P-Tile ES0 FPGA Development Kit Intel Stratix 10 DX P-Tile Production FPGA Development Kit |

This option provides supports for various Development Kits listed. The details of Intel FPGA Development kits can be found on Intel FPGA website. If this menu is grayed out, it is because no board is supported for the options selected (for example, synthesis deselected). If an Intel FPGA Development board is selected, the Target Device used for generation is the one that matches the device on the Development Kit

Note: No development kit supported for F-Tile

|

|

| Currently Selected Example Design |

PIO using MQDMA Bypass mode Device-side Packet Loopback Packet Generate/Check AVMM DMA Traffic Generator/Checker |

Based on parameterization, you can select the appropriate example design.

MCDMA AVST I/F:

MCDMA AVMM I/F:

Bursting Master:

BAM+BAS

BAM+MCDMA AVMM I/F:

BAM+MCDMA AVST I/F:

|