Visible to Intel only — GUID: eis1411549358671

Ixiasoft

Visible to Intel only — GUID: eis1411549358671

Ixiasoft

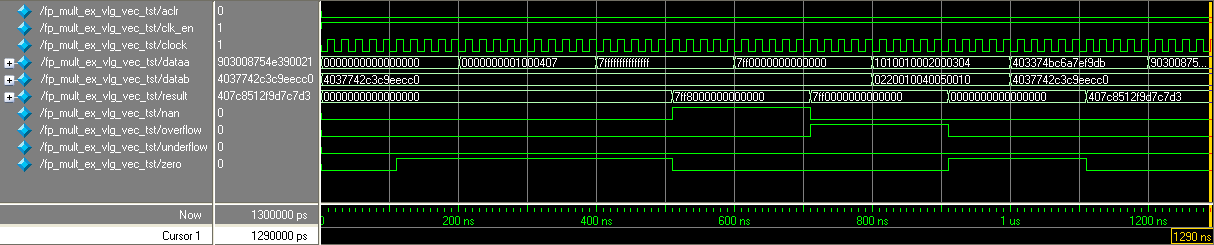

5.5.1. ALTFP_MULT Design Example: Understanding the Simulation Waveform

This design example implements a floating-point multiplier for the multiplication of double-precision format numbers. All the optional input ports (clk_en and aclr) and output ports (overflow, underflow, zero, and nan) are enabled.

In this example, the latency is set to 6 clock cycles. Therefore, every multiplication result appears at the result port 6 clock cycles later.

| Time | Event |

|---|---|

| 0 ns, start-up | dataa[] value: 0000 0000 0000 0000h datab[] value: 4037 742C 3C9E ECC0h Output value: All values seen on the output port before the 6th clock cycle are merely due to the behavior of the system during start-up and should be disregarded. |

| 110 ns | Output value: 0000 0000 0000 0000h Exception handling ports: zero asserts The multiplication of zero at the input port dataa[], and a non-zero value at the input port datab[] results in a zero. |

| 600 ns | dataa[] value: 7FF0 0000 0000 0000h datab[] value: 4037 742C 3C9E ECC0h This is the multiplication of an infinity value and a normal value. |

| 710 ns | Output value: 7FF0 0000 0000 0000h Exception handling ports: overflow asserts The multiplication of an infinity value and a normal value results in infinity. All multiplications with an infinity value results in infinity except when infinity is multiplied with a zero. |