Visible to Intel only — GUID: wak1606925312503

Ixiasoft

Visible to Intel only — GUID: wak1606925312503

Ixiasoft

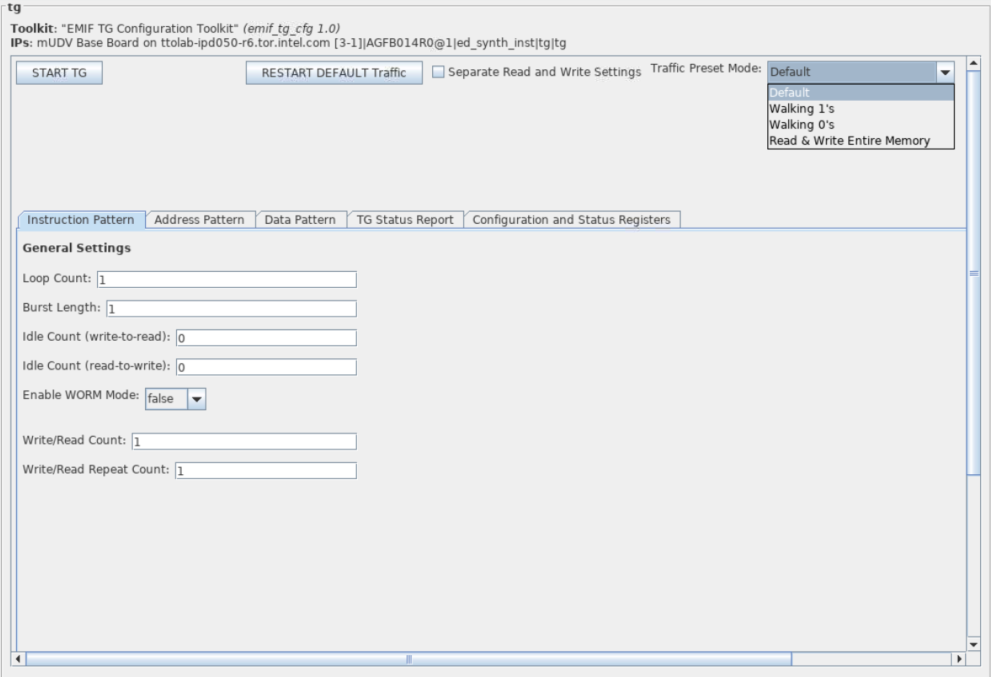

13.9.8.3. Traffic Generator Preset Selection

You can select presets to choose between several different configurations that generate specific traffic patterns on the EMIF control interface. When you select a preset from the drop-down menu, the instruction, address, and data pattern registers are set to generate the desired traffic pattern. The available presets are Default, Walking 1s, Walking 0s, and Read & Write Entire Memory.

Default Preset

The Default preset loads the default values to the configuration registers. This sets the traffic generator to perform one read and one write at address 0 using the data seed 0x5a5a5a5a.

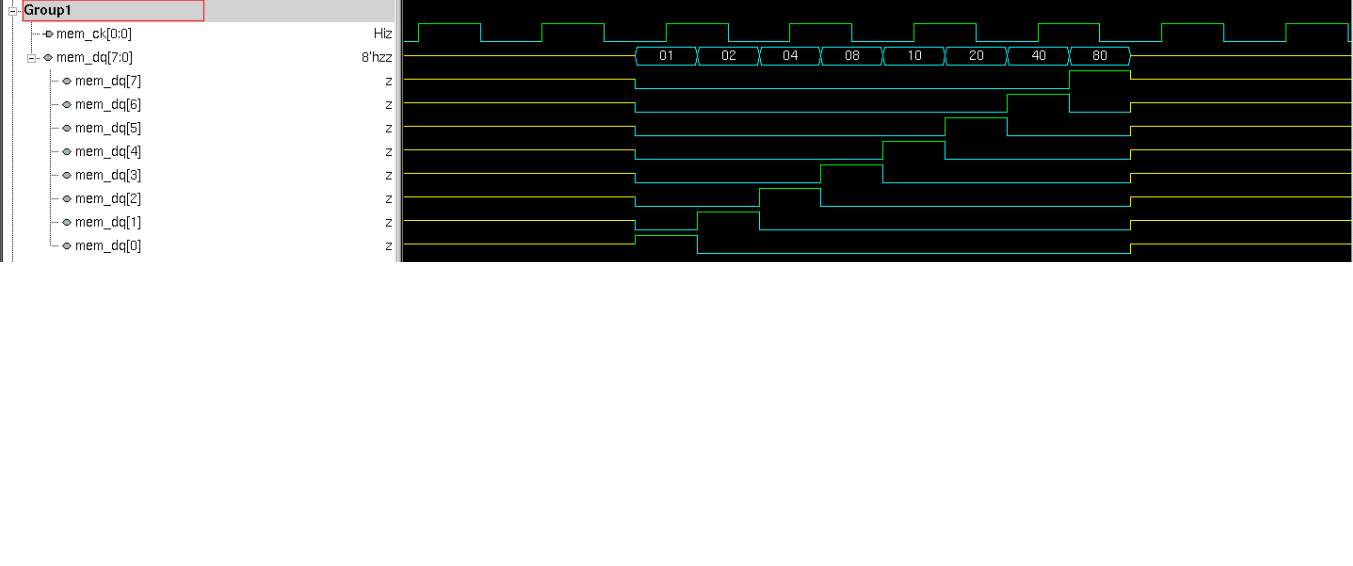

Walking 1s Preset

The Walking 1s preset configures TG2 to produce a “walking” data pattern on the DQ lines by incrementally setting one DQ pin in a DQS group to 1 each clock cycle. This causes the 1 to appear as though it were walking across the DQ pins. The Walking 1s preset starts at address 0 and performs 1 write followed by 1 read for 10 loops.

The following image shows the Walking 1s pattern on the DQ pins of a x8 device.

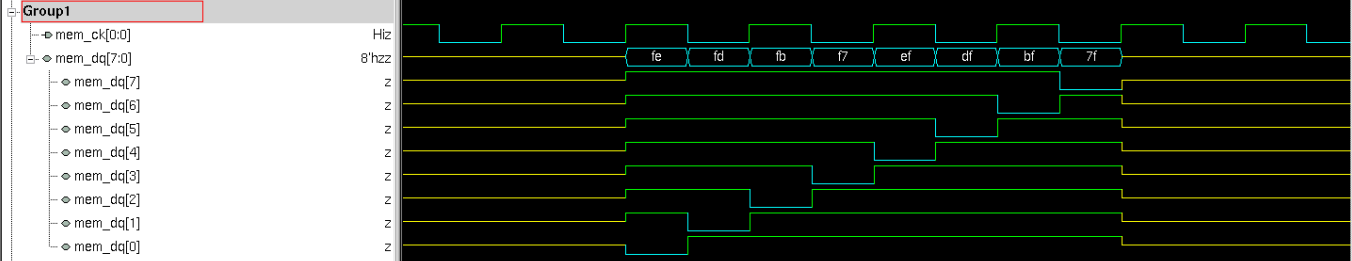

Walking 0s Preset

The Walking 0s preset is the complement of the Walking 1s preset.

The image below illustrates the Walking 0s pattern on the DQ pins of a x8 device.

Read & Write Entire Memory

The Read & Write Entire Memory preset navigates the entire memory sequentially. The data pattern fills all memory locations with 1s. The address pattern sets the burst count to 64 and chooses the loop count and read/write count such that all memory locations are traversed.