Intel® Quartus® Prime Pro Edition User Guide: Design Optimization

A newer version of this document is available. Customers should click here to go to the newest version.

7.3.7.1. Empty Logic Lock Regions

Some reasons to use empty Logic Lock regions are:

- Preliminary floorplanning.

- Complex incremental builds.

- Team based design and interconnect logic.

- Confining logic placements.

Since Logic Lock regions do not reserve any routing resources, the Fitter may use the area for routing purposes.

Use the Core Only attribute for empty Logic Lock regions. When you include periphery resources in empty regions, you restrict the periphery component placement, which can result in a no fit design. After you name the empty region, you can perform the same manipulations as with any populated Logic Lock Region.

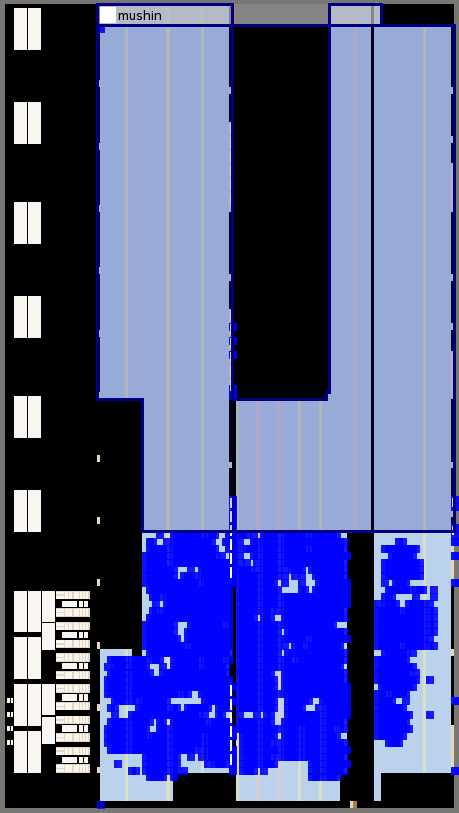

The figure shows an empty Logic Lock region and the logic around it. However, some IOs, HSSIO, and PLLs are in the empty region. This placement happens because the output port connects to the IO, and the IO is always part of the root_partition (top-level partition).