1.3.4. Deterministic Latency (Subclass 1)

The figure below shows the block diagram of deterministic latency test setup. A SYSREF generator provides a periodic SYSREF pulse for both the AD9691 and JESD204B IP Core. The SYSREF generator is running in link clock domain and the period of SYSREF pulse is configured to the desired multiframe size. The SYSREF pulse restarts the LMF counter and realigns it to the LMFC boundary.

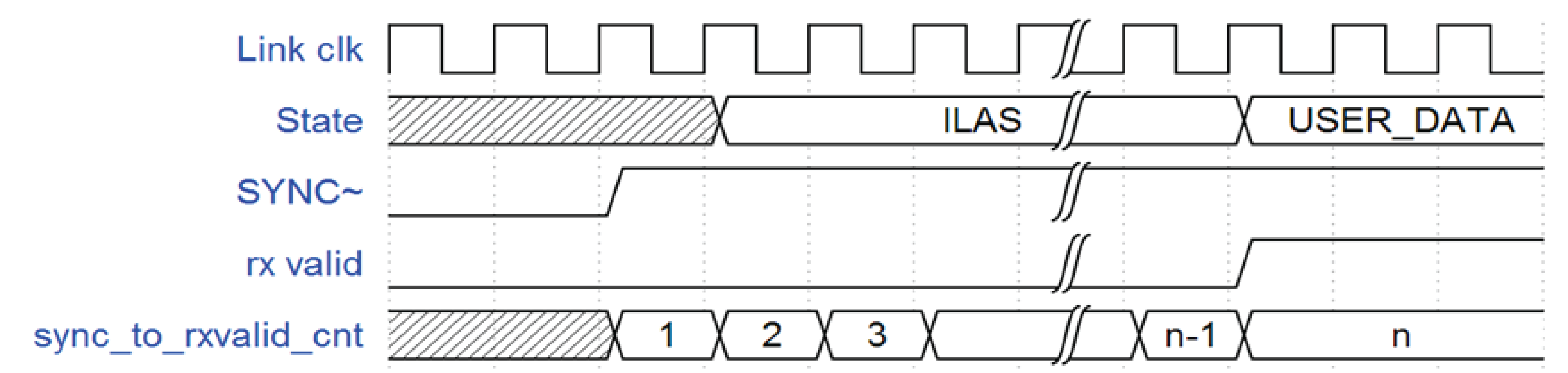

The deterministic latency measurement block checks deterministic latency. This is done by measuring the number of link clock counts between the start of de-assertion of SYNC to the first user data output (assertion of rx_valid). Figure 5 shows the deterministic latency measurement timing diagram.

With the setup above, four test cases were defined to prove deterministic latency. By default, the JESD204B IP Core does single SYSREF detection. The SYSREF N-shot mode is enabled on the AD9691 for this deterministic measurement.

| Test Case | Objective | Description | Passing Criteria |

|---|---|---|---|

| DL.1 |

Check the FPGA SYSREF single detection. |

Check that the FPGA detects the first rising edge of SYSREF pulse. Read the status of sysref_singledet (bit[2]) identifier in syncn_sysref_ctrl register at address 0x54. |

The value of sysref_singledet identifier should be zero. |

| DL.2 |

Check the SYSREF capture. |

Check that FPGA and ADC capture SYSREF correctly and restart the LMF counter. Both FPGA and ADC are also repetitively reset. Read the value of rbd_count (bit[10:3]) identifier in rx_status0 register at address 0x80. |

If the SYSREF is captured correctly and the LMF counter restarts, for every reset, the rbd_count value should only drift a little due to word alignment. |

| DL.3 |

Check the latency from start of SYNC~ deassertion to first user data output. |

Check that the latency is fixed for every FPGA and ADC reset and power cycle. Record the number of link clocks count from the start of SYNC~ deassertion to the first user data output, which is the assertion of jesd204_rx_link_valid signal. |

Consistent latency from the start of SYNC~ deassertion to the assertion of jesd204_rx_link_valid signal. |

| DL.4 |

Check the data latency during user data phase. |

Check that the data latency is fixed during user data phase. Observe the ramp pattern from the Signal Tap Logic Analyzer. |

The ramp pattern should be in perfect shape with no distortion. |