Visible to Intel only — GUID: nik1410905312703

Ixiasoft

1. Datasheet

2. Getting Started with the Avalon-MM DMA

3. Parameter Settings

4. Registers

5. Error Handling

6. PCI Express Protocol Stack

7. V-Series Avalon-MM DMA for PCI Express

8. Transceiver PHY IP Reconfiguration

A. Frequently Asked Questions for V-Series Avalon-MM DMA Interface for PCIe

B. V-Series Interface for PCIe Solutions User Guide Archive

C. Document Revision History

1.1. V-Series Avalon-MM DMA Interface for PCIe* Datasheet

1.2. Features

1.3. Comparison of Avalon-ST, Avalon-MM and Avalon-MM with DMA Interfaces for V-Series Devices

1.4. Release Information

1.5. V-Series Device Family Support

1.6. Design Examples

1.7. Debug Features

1.8. IP Core Verification

1.9. Resource Utilization

1.10. V-Series Recommended Speed Grades

1.11. Creating a Design for PCI Express

4.1. Correspondence between Configuration Space Registers and the PCIe Specification

4.2. Type 0 Configuration Space Registers

4.3. Type 1 Configuration Space Registers

4.4. PCI Express Capability Structures

4.5. Intel-Defined VSEC Registers

4.6. Advanced Error Reporting Capability

4.7. DMA Descriptor Controller Registers

4.8. Control Register Access (CRA) Avalon-MM Slave Port

Visible to Intel only — GUID: nik1410905312703

Ixiasoft

2.2. Generating the Testbench

- Copy the example design, pcie_de_ep_dma_g3x8_integrated.qsys, from the installation directory: <install_dir>/ip/altera/altera_pcie/altera_pcie_hip_256_avmm/example_design/ to your working directory.

- Start Platform Designer, by typing the following command:

qsys-edit

- Open pcie_de_ep_dma_g3x8_integrated.qsys.

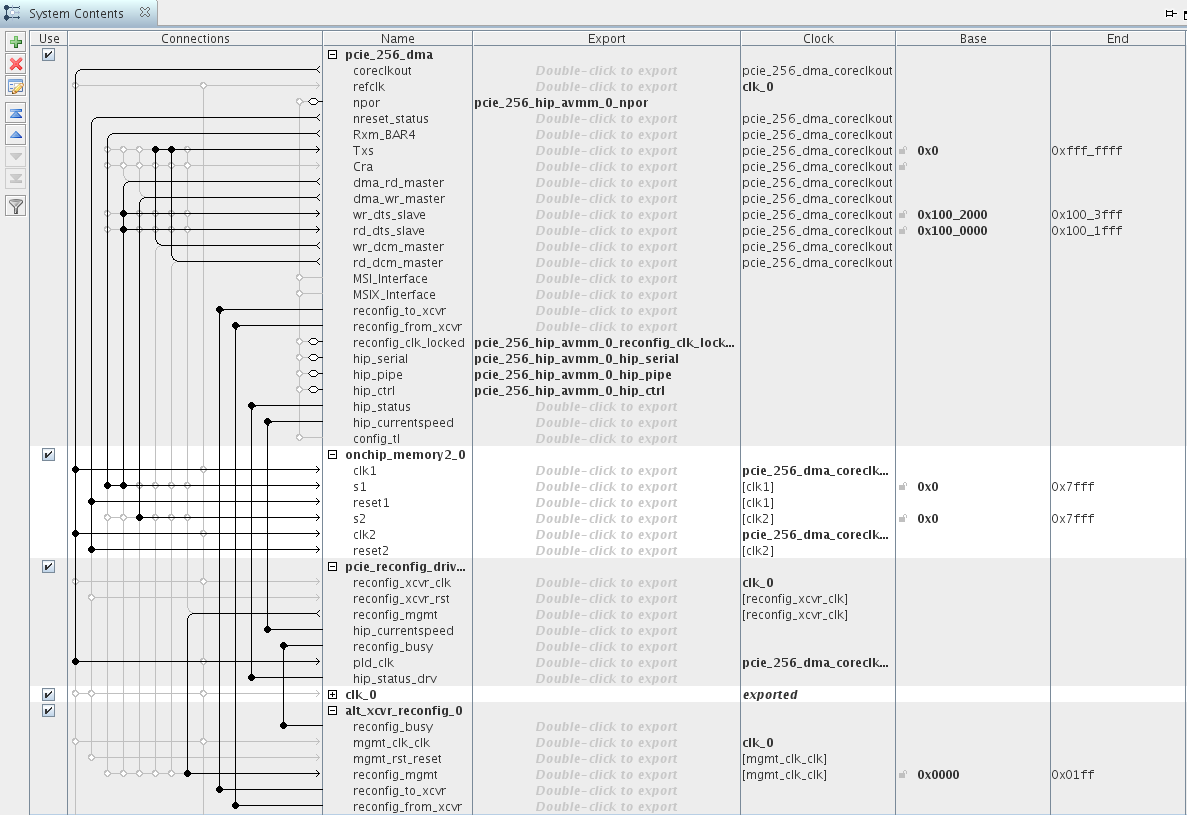

The following figure shows the Platform Designer system.

Figure 2. V-Series Avalon-MM DMA for PCI Express Platform Designer System Design

- Click Generate > Generate Testbench System.

- Specify the following parameters:

Table 13. Parameters to Specify in the Generation Dialog Box Parameter

Value

Testbench System

Create testbench Platform Designer system

Standard, BFMs for standard Platform Designer interfaces

Create testbench simulation model

Verilog

Allow mixed-language simulation You can leave this option off. Output Directory

Path

<working_dir>//pcie_de_ep_dma_g3x8_integrated - Click Generate.