Visible to Intel only — GUID: msn1613079065191

Ixiasoft

Visible to Intel only — GUID: msn1613079065191

Ixiasoft

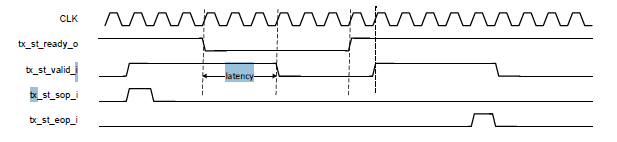

4.4.1.4.1. Avalon® Streaming TX Interface tx_st_ready_o Behavior

The following timing diagram illustrates the behavior of tx_st_ready_o, which is deasserted to pause the data transmission to the Transaction Layer of the R-tile IP for PCIe, and then reasserted. As an example, the timing diagram shows a readyLatency of three cycles. The application deasserts tx_st_valid_i three cycles after tx_st_ready_o is deasserted. Refer to the Avalon® Interface Specifications for a detailed definition of readyLatency.

The maximum latency between the deassertion of tx_st_ready_o and tx_st_valid_i is 16 cycles.

The application must not deassert tx_st_valid_i between tx_st_sop_i and tx_st_eop_i on a ready cycle unless there is backpressure from the R-tile PCIe IP indicated by the deassertion of tx_st_ready_o. For the definition of a ready cycle, refer to the Avalon Interface Specifications.