Visible to Intel only — GUID: psj1612899669712

Ixiasoft

Visible to Intel only — GUID: psj1612899669712

Ixiasoft

4.4.7. Configuration Intercept Interface

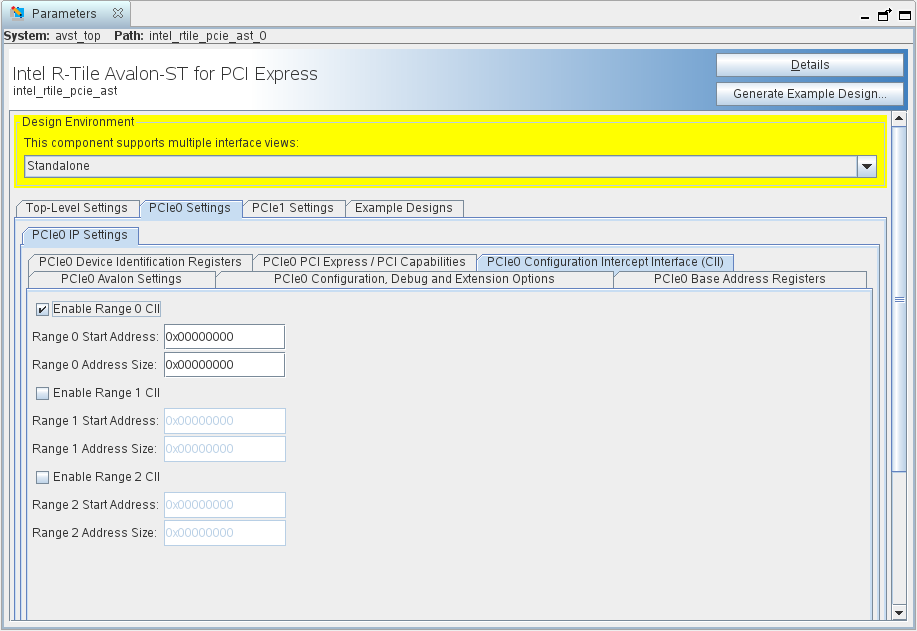

The Configuration Intercept Interface (CII) allows the application logic to detect the occurrence of a Configuration (CFG) request on the link and to modify its behavior. To provide further flexibility, the R-Tile Intel FPGA IP for PCI Express allows you to define up to three different PCIe configuration space ranges to intercept using this interface (refer to Figure 31, where the allowed range is 0x - 0xFFF).

The application logic should detect the CFG request at the rising edge of cii_req_o. Due to the latency of the EMIB, the cii_req_o can be deasserted many cycles after the deassertion of cii_halt_i.

The application logic can use the CII to:

- Delay the processing of a CFG request by the controller. This allows the application to perform any housekeeping task first.

- Overwrite the data payload of a CfgWr request. The application logic can also overwrite the data payload of a CfgRd Completion TLP.

This interface also allows you to implement the Intel Vendor Specific Extended Capability (VSEC) registers. All configuration accesses targeting the Intel VSEC registers (addresses 0xD00 to 0xFFF) are automatically mapped to this interface and can be monitored via this interface.

If you are not using this interface, tie cii_halt_p0/1 to logic 0.

| Signal Name | Direction | Description | EP/RP/BP | Clock Domain |

|---|---|---|---|---|

| pX_cii_req_o | Output | Indicates the CFG request is intercepted and all the other CII signals are valid. | EP | slow_clk |

| pX_cii_hdr_poisoned_o | Output | The poisoned bit in the received TLP header on the CII. | EP | slow_clk |

| pX_cii_hdr_first_be_o[3:0] | Output | The first dword byte enable field in the received TLP header on the CII. | EP | slow_clk |

| pX_cii_func_num_o[2:0] | Output | The function number in the received TLP header on the CII. | EP | slow_clk |

| pX_cii_wr_o | Output | Indicates that cii_dout_p0/1 is valid. This signal is asserted only for a configuration write request. | EP | slow_clk |

| pX_cii_wr_vf_active_o | Output | Indicates that the received TLP targets a virtual function (VF) inside the controller, which is identified by cii_vf_num_o[10:0]. | EP | slow_clk |

| pX_cii_vf_num_o[10:0] | Output | Identifies the VF inside the controller that was targeted. | EP | slow_clk |

| pX_cii_addr_o[9:0] | Output | The double-word register address in the received TLP header on the CII. | EP | slow_clk |

| pX_cii_dout_o[31:0] | Output | Received TLP payload data from the link partner to your application client. The data is in little endian format. The first received payload byte is in bits [7:0]. | EP | slow_clk |

| pX_cii_override_en_i | Input | Override enable. When the application logic asserts this input, the PCIe Hard IP overrides the CfgWr payload or CfgRd completion using the data supplied by the application logic on cii_override_din_i[31:0]. | EP | slow_clk |

| pX_cii_override_din_i[31:0] | Input | Override data.

|

EP | slow_clk |

| pX_cii_halt_i | Input | Flow control input signal. When cii_halt_p0/1 is asserted, the PCIe Hard IP halts the processing of CFG requests for the PCIe configuration space registers. | EP | slow_clk |