Visible to Intel only — GUID: ytj1533931508178

Ixiasoft

3.1. Viewing Basic Project Information

3.2. Intel® Quartus® Prime Project Contents

3.3. Managing Project Settings

3.4. Managing Logic Design Files

3.5. Managing Timing Constraints

3.6. Integrating Other EDA Tools

3.7. Exporting Compilation Results

3.8. Migrating Projects Across Operating Systems

3.9. Archiving Projects

3.10. Command-Line Interface

3.11. Managing Projects Revision History

3.7.1. Exporting a Version-Compatible Compilation Database

3.7.2. Importing a Version-Compatible Compilation Database

3.7.3. Creating a Design Partition

3.7.4. Exporting a Design Partition

3.7.5. Reusing a Design Partition

3.7.6. Viewing Quartus Database File Information

3.7.7. Clearing Compilation Results

4.1. Design Planning

4.2. Create a Design Specification and Test Plan

4.3. Plan for the Target Device

4.4. Plan for Intellectual Property Cores

4.5. Plan for Standard Interfaces

4.6. Plan for Device Programming

4.7. Plan for Device Power Consumption

4.8. Plan for Interface I/O Pins

4.9. Plan for other EDA Tools

4.10. Plan for On-Chip Debugging Tools

4.11. Plan HDL Coding Styles

4.12. Plan for Hierarchical and Team-Based Designs

4.13. Design Planning Revision History

5.1. IP Catalog and Parameter Editor

5.2. Installing and Licensing Intel® FPGA IP Cores

5.3. IP General Settings

5.4. Adding IP to IP Catalog

5.5. Best Practices for Intel® FPGA IP

5.6. Specifying the IP Core Parameters and Options ( Intel® Quartus® Prime Pro Edition)

5.7. Modifying an IP Variation

5.8. Upgrading IP Cores

5.9. Simulating Intel® FPGA IP Cores

5.10. Generating Simulation Files for Platform Designer Systems and IP Variants

5.11. Synthesizing IP Cores in Other EDA Tools

5.12. Instantiating IP Cores in HDL

5.13. Support for the IEEE 1735 Encryption Standard

5.14. Introduction to Intel FPGA IP Cores Revision History

6.2.1. Modify Entity Name Assignments

6.2.2. Resolve Timing Constraint Entity Names

6.2.3. Verify Generated Node Name Assignments

6.2.4. Replace Logic Lock (Standard) Regions

6.2.5. Modify Signal Tap Logic Analyzer Files

6.2.6. Remove References to .qip Files

6.2.7. Remove Unsupported Feature Assignments

6.4.1. Verify Verilog Compilation Unit

6.4.2. Update Entity Auto-Discovery

6.4.3. Ensure Distinct VHDL Namespace for Each Library

6.4.4. Remove Unsupported Parameter Passing

6.4.5. Remove Unsized Constant from WYSIWYG Instantiation

6.4.6. Remove Non-Standard Pragmas

6.4.7. Declare Objects Before Initial Values

6.4.8. Confine SystemVerilog Features to SystemVerilog Files

6.4.9. Avoid Assignment Mixing in Always Blocks

6.4.10. Avoid Unconnected, Non-Existent Ports

6.4.11. Avoid Illegal Parameter Ranges

6.4.12. Update Verilog HDL and VHDL Type Mapping

Visible to Intel only — GUID: ytj1533931508178

Ixiasoft

3.7.3. Creating a Design Partition

A design partition is a logical, named, hierarchical boundary that you can assign to an instance in your design. Defining a design partition allows you to optimize and lock down the compilation results for individual blocks. You can then optionally export the compilation results of a design partition for reuse in another context, such as reuse in another project.

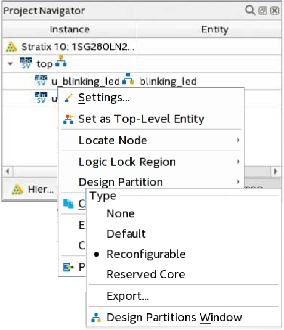

Figure 23. Design Partitions in Design Hierarchy

Follow these steps to create and modify design partitions:

- In the Intel® Quartus® Prime software, open the project that you want to partition.

- Generate synthesis or final compilation results by running one of the following commands:

- Click Processing > Start > Start Analysis & Synthesis to generate synthesized compilation results.

- Click Processing > Start Compilation to generate final compilation results.

- In the Project Navigator, right-click an instance in the Hierarchy tab, click Design Partition > Set as Design Partition.

Figure 24. Creating a Design Partition from the Project Hierarchy

- To view and edit all design partitions in the project, click Assignments > Design Partitions Window.

Figure 25. Design Partitions Window

- Specify the properties of the design partition in the Design Partitions Window. The following settings are available:

Table 8. Design Partition Settings Option Description Partition Name Specifies the partition name. Each partition name must be unique and consist of only alphanumeric characters. The Intel® Quartus® Prime software automatically creates a top-level (|) "root_partition" for each project revision. Hierarchy Path Specifies the hierarchy path of the entity instance that you assign to the partition. You specify this value in the Create New Partition dialog box. The root partition hierarchy path is |. Type Double-click to specify one of the following partition types that control how the Compiler processes and implements the partition: - Default—Identifies a standard partition. The Compiler processes the partition using the associated design source files.

- Reconfigurable—Identifies a reconfigurable partition in a partial reconfiguration flow. Specify the Reconfigurable type to preserve synthesis results, while allowing refit of the partition in the PR flow.

- Reserved Core—Identifies a partition in a block-based design flow that is reserved for core development by a Consumer reusing the device periphery.

Preservation Level Specifies one of the following preservation levels for the partition: - Not Set—specifies no preservation level. The partition compiles from source files.

- synthesized—the partition compiles using the synthesized snapshot.

- final—the partition compiles using the final snapshot.

With Preservation Level of synthesized or final, changes to the source code do not appear in the synthesis.

Empty Specifies an empty partition that the Compiler skips. This setting is incompatible with the Reserved Core and Partition Database File settings for the same partition. The Preservation Level must be Not Set. An empty partition cannot have any child partitions. Partition Database File Specifies a Partition Database File (.qdb) that the Compiler uses during compilation of the partition. You export the .qdb for the stage of compilation that you want to reuse (synthesized or final). Assign the .qdb to a partition to reuse those results in another context. Entity Re-binding - PR Flow—specifies the entity that replaces the default persona in each implementation revision.

- Root Partition Reuse Flow —specifies the entity that replaces the reserved core logic in the consumer project.

Color Specifies the color-coding of the partition in the Chip Planner and Design Partition Planner displays. Post Synthesis Export File Automatically exports post-synthesis compilation results for the partition to the specified .qdb file each time Analysis & Synthesis runs. You can automatically export any design partition that does not have a preserved parent partition, including the root_partition. Post Final Export File Automatically exports post-final compilation results for the partition to the specified .qdb file each time the final stage of the Fitter runs. You can automatically export any design partition that does not have a preserved parent partition, including the root_partition.