Visible to Intel only — GUID: ziw1505804428480

Ixiasoft

1.5. Compiling and Testing the Design

- Ensure that the hardware design example generation is complete.

- Open quartus/sdi_ii_s10_demo.qpf.

- Click Processing > Start Compilation.

- After successful compilation, the Intel® Quartus® Prime Pro Edition software generates a .sof file in your specified directory.

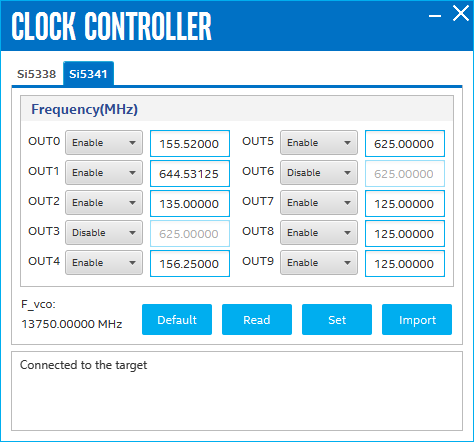

- Open the Clock Controller parameter editor, and set the clock frequency in the Si5341 tab.

- HD/3G-SDI single-rate and triple-rate designs:

- For parallel loopback with external VCXO designs, set Out1 frequency to 148.5 MHz.

- For parallel loopback without external VCXO designs, set Out1 frequency to 100 MHz.

- If you turn on the Dynamic Tx clock switching parameter in the Design Example parameter editor, set Out1 frequency to 148.35165 MHz.

- Multi-rate designs:

- For parallel loopback with external VCXO designs, set Out1 frequency to 148.5 MHz.

- For parallel loopback without external VCXO designs, set Out4 frequency to 148.5 MHz, and set Out5 frequency to 245 MHz.

- If you turn on the Dynamic Tx clock switching parameter in the Design Example parameter editor, set Out4 frequency to 148.3516 MHz, and set Out5 frequency to 148.5 MHz.

Figure 5. Clock Controller - Si5341

- HD/3G-SDI single-rate and triple-rate designs:

- Configure the selected device on the development board using the generated .sof file (Tools > Programmer ).

Note: If you missed setting the clock controller and program the device within 18 seconds, you will get an error message. In this case, power cycle the development board and program the .sof file first. Then, specify the settings for the clock controller and program the .sof file again.

- For serial loopback designs, open the System Console to control the internal video pattern generator. Click Tools > System Debugging Tools > System Console.

Note: Close the Clock Controller GUI and the Programmer window before you open the System Console.

- After the initialization, type source ../hwtest/tpg_ctrl.tcl in the System Console to open the pattern generator control user interface. Select your desired video format.