Visible to Intel only — GUID: cki1481303811037

Ixiasoft

Visible to Intel only — GUID: cki1481303811037

Ixiasoft

3.2.2. HPS I/O Settings: Constraints and Drive Strengths

GUIDELINE: Ensure that you have I/O settings for the HPS Dedicated I/O (drive strength, I/O standard, weak pull-up enable, etc.)

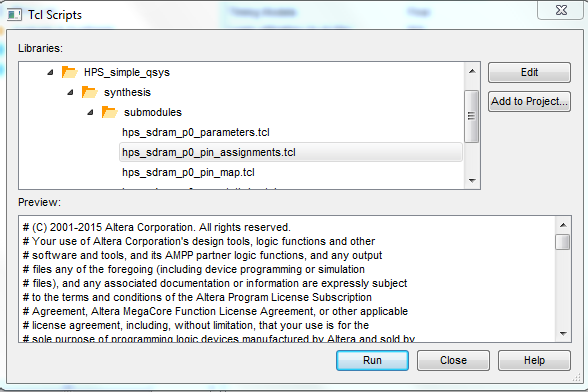

The HPS pin location assignments are managed automatically when you generate the Platform Designer (Standard) system containing the HPS. As for the HPS SDRAM, the I/O standard and termination settings are done once you run the “hps_sdram_p0_pin_assignments.tcl” script that is created once the Platform Designer (Standard) HPS Component has been generated.

The only HPS I/O constraints you must manage are for HPS Dedicated Function Pins and HPS Dedicated I/O. Constraints such as drive strength, I/O standards, and weak pull-up enables are added to the Intel® Quartus® Prime project just like FPGA constraints and are applied to the HPS at boot time when the second stage bootloader configures the I/O. For FPGA I/O, the I/O constraints are applied to the FPGA configuration file.